Usb interrupt system – Rainbow Electronics AT89C5132 User Manual

Page 71

71

AT8xC5132

4173A–8051–08/02

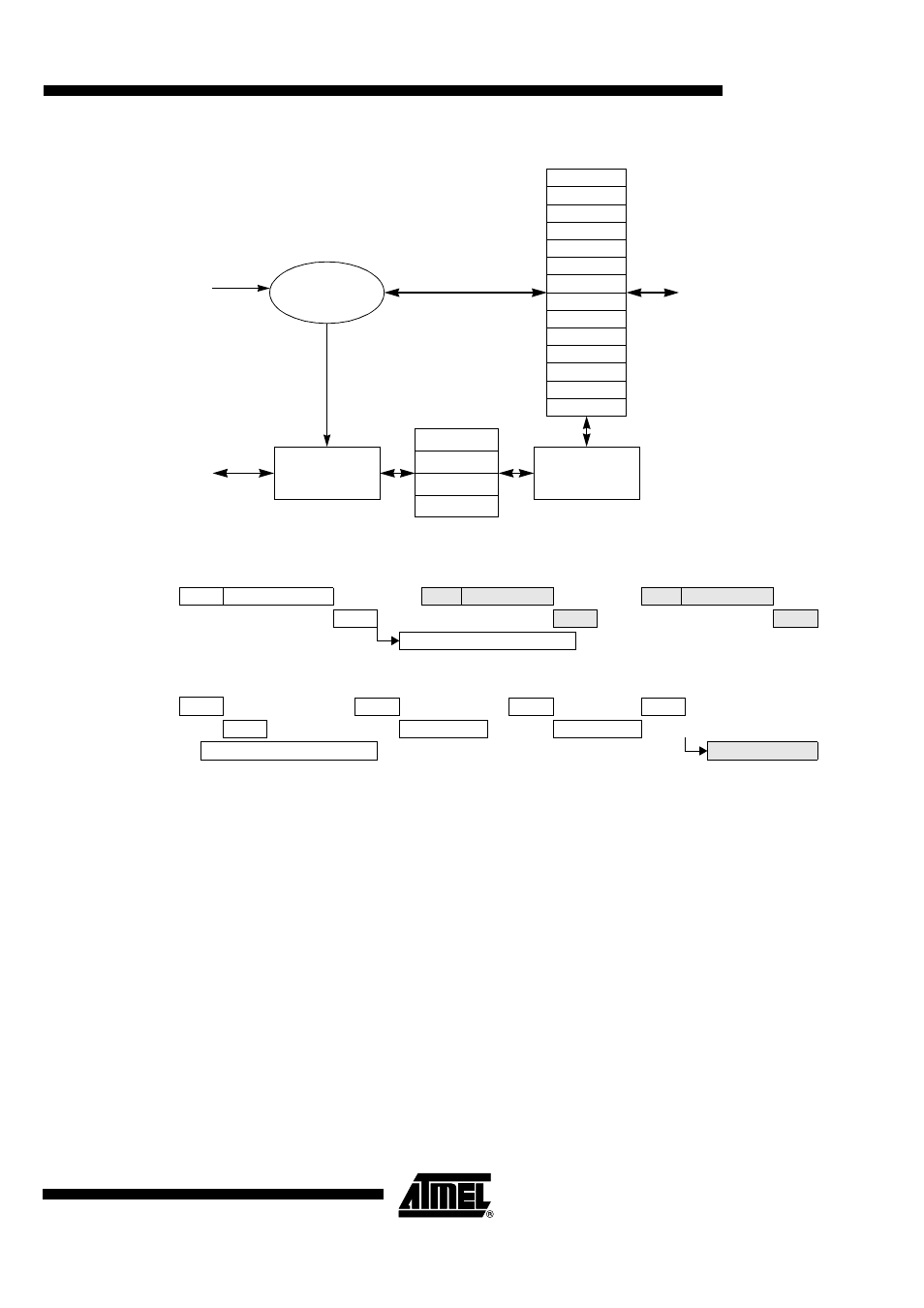

Figure 49. UFI Block Diagram

Figure 50. USB Typical Transaction Load

USB Interrupt System

As shown in Figure 51, the USB controller of the AT8xC5132 handle sixteen interrupt

sources. These sources are separated in two groups: the endpoints interrupts and the

controller interrupts, combined together to appear as single interrupt source for the C51

core. The USB interrupt is enabled by setting the EUSB bit in IEN1.

Controller Interrupt Sources

There are four controller interrupt sources which can be enabled separately in USBIEN:

•

SPINT: Suspend Interrupt Flag.

This flag triggers an interrupt when a USB Suspend (Idle bus for three frame

periods: a J state for 3 ms) is detected.

•

SOFINT: Start Of Frame Interrupt Flag.

This flag triggers an interrupt when a USB start of frame packet has been received.

•

EORINT: End Of Reset Interrupt Flag.

This flag triggers an interrupt when a End Of Reset has been detected by the USB

controller.

•

WUPCPU: Wake Up CPU Interrupt Flag.

This flag triggers an interrupt when the USB controller is in SUSPEND state and is

re-activated by a non-idle signal from USB line.

To/From C51 Core

Endpoint Control

C51 side

Endpoint Control

USB side

Endpoint 3

Endpoint 2

Endpoint 1

Endpoint 0

USBCON

USBINT

USBIEN

UEPINT

UEPIEN

UEPNUM

UEPSTAX

USBADDR

UEPCONX

UEPDATX

UEPRST

UBYCTX

UFNUMH

UFNUML

Asynchronous Information

Transfer

Control

FSM

To/From SIE

12 MHz DPLL

OUT Transactions:

HOST

UFI

C51

OUT

DATA0 (n Bytes)

ACK

Endpoint FIFO read (n Bytes)

OUT

DATA1

NACK

OUT

DATA1

ACK

IN Transactions:

HOST

UFI

C51

IN

ACK

Endpoint FIFO write

IN

DATA1

NACK

C51 interrupt

IN

DATA1

C51 interrupt

Endpoint FIFO write