Registers, Table 57) – Rainbow Electronics AT89C5132 User Manual

Page 49

49

AT8xC5132

4173A–8051–08/02

reset algorithm takes control. Reset initializes the AT8xC5132 and vectors

the CPU to address 0000h.

Notes:

1. During the time that execution resumes, the internal RAM cannot be accessed; how-

ever, it is possible for the Port pins to be accessed. To avoid unexpected outputs at

the Port pins, the instruction immediately following the instruction that activated the

Power-down mode should not write to a Port pin or to the external RAM.

2. Exit from power-down by reset redefines all the SFRs, but does not affect the internal

RAM content.

Registers

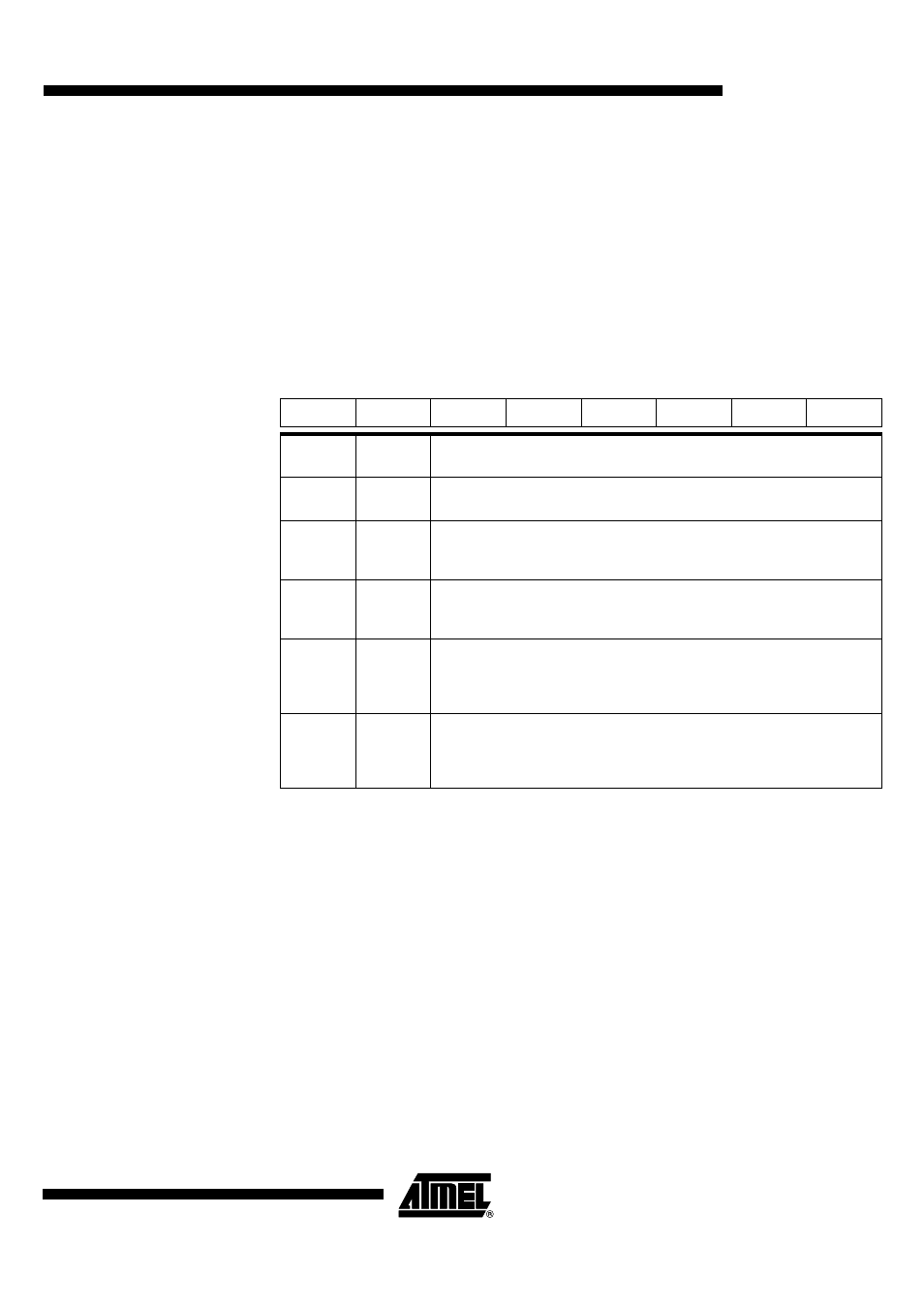

Table 57. PCON Register

PCON (S:87h) – Power Configuration Register

Reset Value = XXXX 0000b

7

6

5

4

3

2

1

0

-

-

-

-

GF1

GF0

PD

IDL

Bit

Number

Bit

Mnemonic

Description

7 - 4

-

Reserved

The values read from these Bits are indeterminate. Do not set these Bits.

3

GF1

General-purpose flag 1

One use is to indicate whether an interrupt occurred during normal operation or

during Idle mode.

2

GF0

General-purpose flag 0

One use is to indicate whether an interrupt occurred during normal operation or

during Idle mode.

1

PD

Power-down Mode bit

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Power-down mode.

If IDL and PD are both set, PD takes precedence.

0

IDL

Idle Mode bit

Cleared by hardware when an interrupt or reset occurs.

Set to activate the Idle mode.

If IDL and PD are both set, PD takes precedence.