Watchdog timer, Description, Watchdog clock controller – Rainbow Electronics AT89C5132 User Manual

Page 58

58

AT8xC5132

4173A–8051–08/02

Watchdog Timer

The AT8xC5132 implement a hardware Watchdog Timer (WDT) that automatically

resets the chip if it is allowed to time out. The WDT provides a means of recovering from

routines that do not complete successfully due to software or hardware malfunctions.

Description

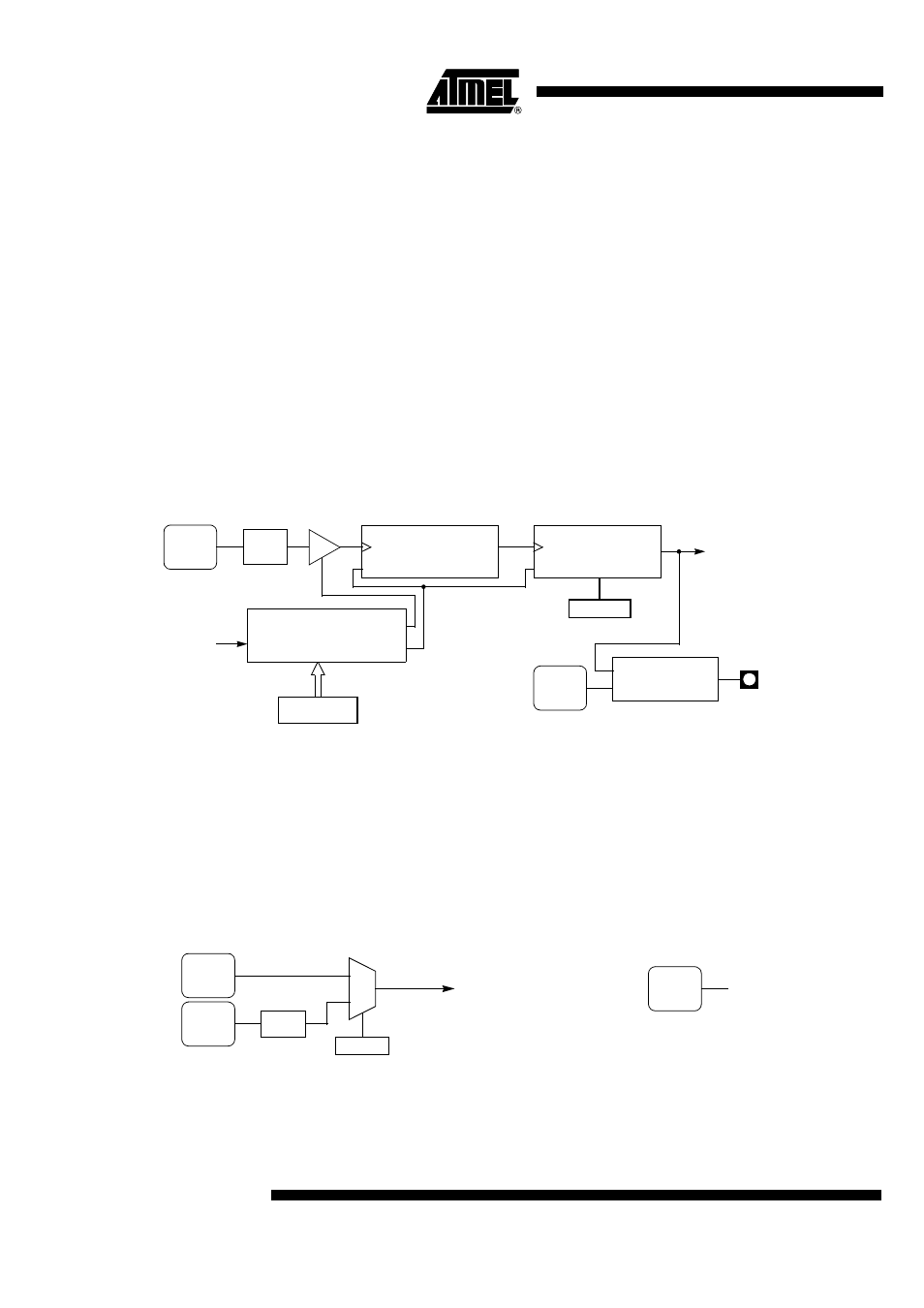

The WDT consists of a 14-bit prescaler followed by a 7-bit programmable counter. As

shown in Figure 37, the 14-bit prescaler is fed by the WDT clock detailed in section

"Watchdog Clock Controller", page 58.

The Watchdog Timer Reset register (WDTRST, see Table 64) provides control access

to the WDT, while the Watchdog Timer Program register (WDTPRG, see Figure 65) pro-

vides time-out period programming.

Three operations control the WDT:

•

Chip reset clears and disables the WDT.

•

Programming the time-out value to the WDTPRG register.

•

Writing a specific two-byte sequence to the WDTRST register clears and enables

the WDT.

Figure 37. WDT Block Diagram

Watchdog Clock

Controller

As shown in Figure 38 the WDT clock (F

WDT

) is derived from either the peripheral clock

(F

PER

) or the oscillator clock (F

OSC

) depending on the WTX2 bit in CKCON register.

These clocks are issued from the Clock Controller block as detailed in section "Clock

Controller", page 12. When WTX2 bit is set, the WDT clock frequency is fixed and equal

to the oscillator clock frequency divided by 2. When cleared, the WDT clock frequency is

equal to the oscillator clock frequency divided by 2 in standard mode or to the oscillator

clock frequency in X2 mode.

Figure 38. WDT Clock Controller and Symbol

WTO2:0

WDTPRG.2:0

WDT

CLOCK

÷

6

System Reset

1Eh-E1h Decoder

WDTRST

14-bit Prescaler

RST

7-bit Counter

RST

To Internal Reset

EN

RST

MATCH

SET

OV

OSC

CLOCK

RST

Pulse Generator

PER

CLOCK

WDT

CLOCK

OSC

CLOCK

0

1

WTX2

CKCON.6

÷

2

WDT Clock

WDT Clock Symbol