Atmega161(l) – Rainbow Electronics ATmega161L User Manual

Page 86

86

ATmega161(L)

1228C–AVR–08/02

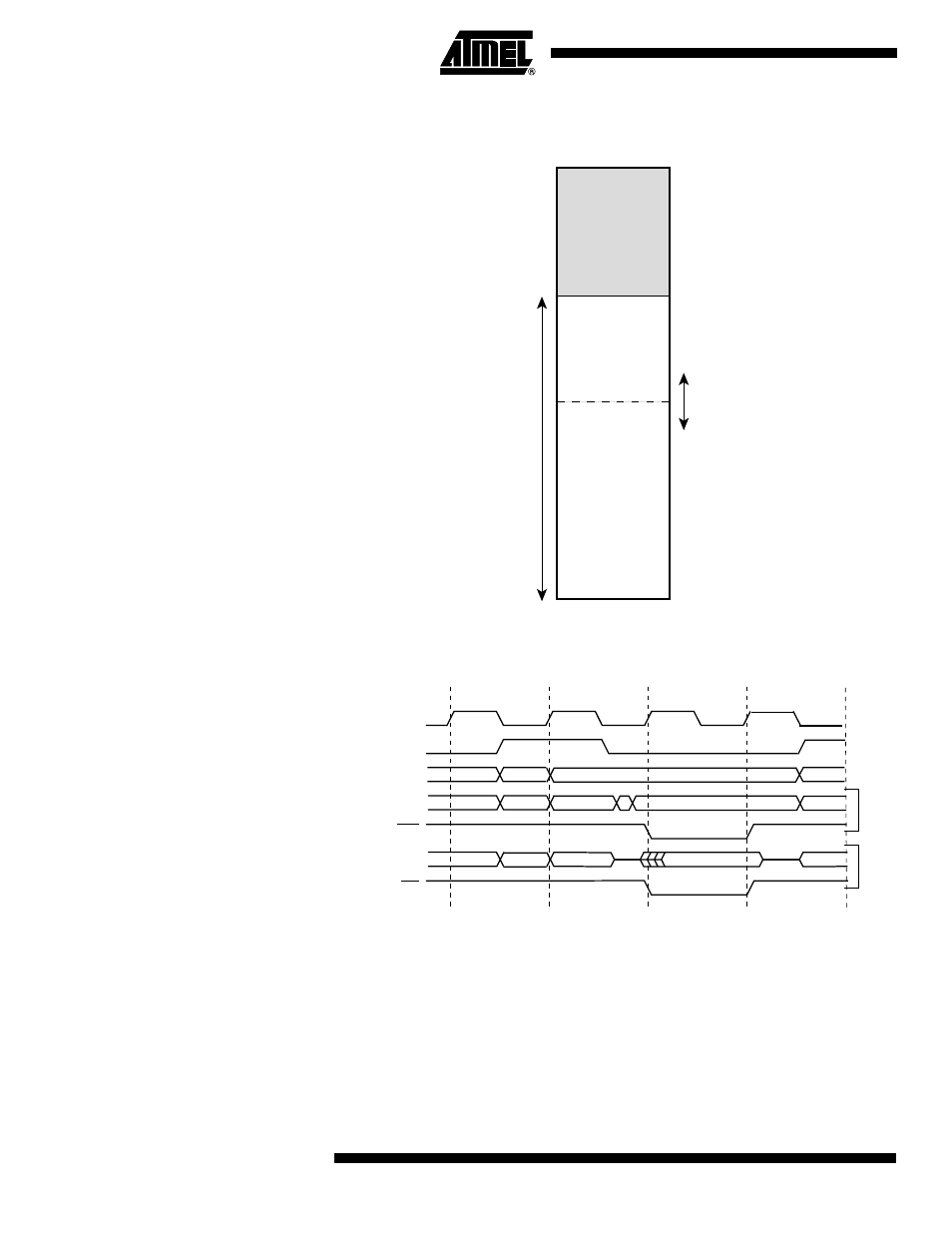

Figure 49. External Memory with Page Select

Figure 50. External Data Memory Cycles without Wait State (SRWn1 = 0 and SRWn0

=0)

(1)

Note:

1. SRWn1 = SRW11 (upper page) or SRW01 (lower page), SRWn0 = SRW10 (upper

page) or SRW00 (lower page).

The ALE pulse in period T4 is only present if the next instruction accesses the RAM

(internal or external). The Data and Address will only change in T4 if ALE is present

(the next instruction accesses the RAM).

$0000

Data Memory

$0460

External Memory

(0-63K x 8)

$FFFF

Internal memory

SRL[2..0]

SRW11

SRW10

SRW01

SRW00

Lower page

Upper page

System Clock Ø

ALE

WR

RD

Data/Address [7..0]

Data/Address [7..0]

Address [15..8]

Address

Address

Address

T1

T2

T3

XX

Data

Data

Wr

ite

Read

T4

XX

XX

XX

XX

Prev. addr.

XX

Prev. data

XX

Prev. data

- MAX5151 (16 pages)

- MAXQ3108 (64 pages)

- MAX5661 (39 pages)

- MAX6691 (7 pages)

- MAX5362 (12 pages)

- ADC10158 (26 pages)

- MAX8922L (14 pages)

- MAX8596Z (8 pages)

- MAX7491 (18 pages)

- MAX15040 (15 pages)

- MAX5177 (16 pages)

- ADC08138 (22 pages)

- MAX5961 (42 pages)

- T89C51RD2 (86 pages)

- MAX16055 (9 pages)

- MAX6659 (17 pages)

- ADC0820 (20 pages)

- MAX6678 (19 pages)

- MAX8884Z (15 pages)

- MAX16915 (9 pages)

- MAX8620 (18 pages)

- MAX5144 (12 pages)

- MAX6670 (8 pages)

- MAX8760 (39 pages)

- W78C32C (14 pages)

- MX7533 (8 pages)

- MAX8727 (13 pages)

- MAX9053 (15 pages)

- W78C54 (16 pages)

- MAX8614B (15 pages)

- W90N740 (219 pages)

- MAX6626 (13 pages)

- ADC10738 (30 pages)

- MAX17000 (31 pages)

- MAX5051 (21 pages)

- MAXQ1004 (18 pages)

- MAX6871 (51 pages)

- MX7847 (12 pages)

- MAX6608 (6 pages)

- MAX17083 (15 pages)

- MAX6641 (17 pages)

- MAX5251 (16 pages)

- MAX6338 (8 pages)

- MAX6690 (16 pages)

- MAX8668 (18 pages)