Uarts, Data transmission, Atmega161(l) – Rainbow Electronics ATmega161L User Manual

Page 69

69

ATmega161(L)

1228C–AVR–08/02

UARTs

The ATmega161 features two full-duplex (separate Receive and Transmit Registers)

Universal Asynchronous Receiver and Transmitters (UARTs). The main features are:

•

Baud Rate Generator Generates any Baud Rate

•

High Baud Rates at low XTAL Frequencies

•

8 or 9 Bits Data

•

Noise Filtering

•

Overrun Detection

•

Framing Error Detection

•

False Start Bit Detection

•

Three Separate Interrupts on TX Complete, TX Data Register Empty, and RX Complete

•

Multi-processor Communication Mode

•

Double-speed UART Mode

Data Transmission

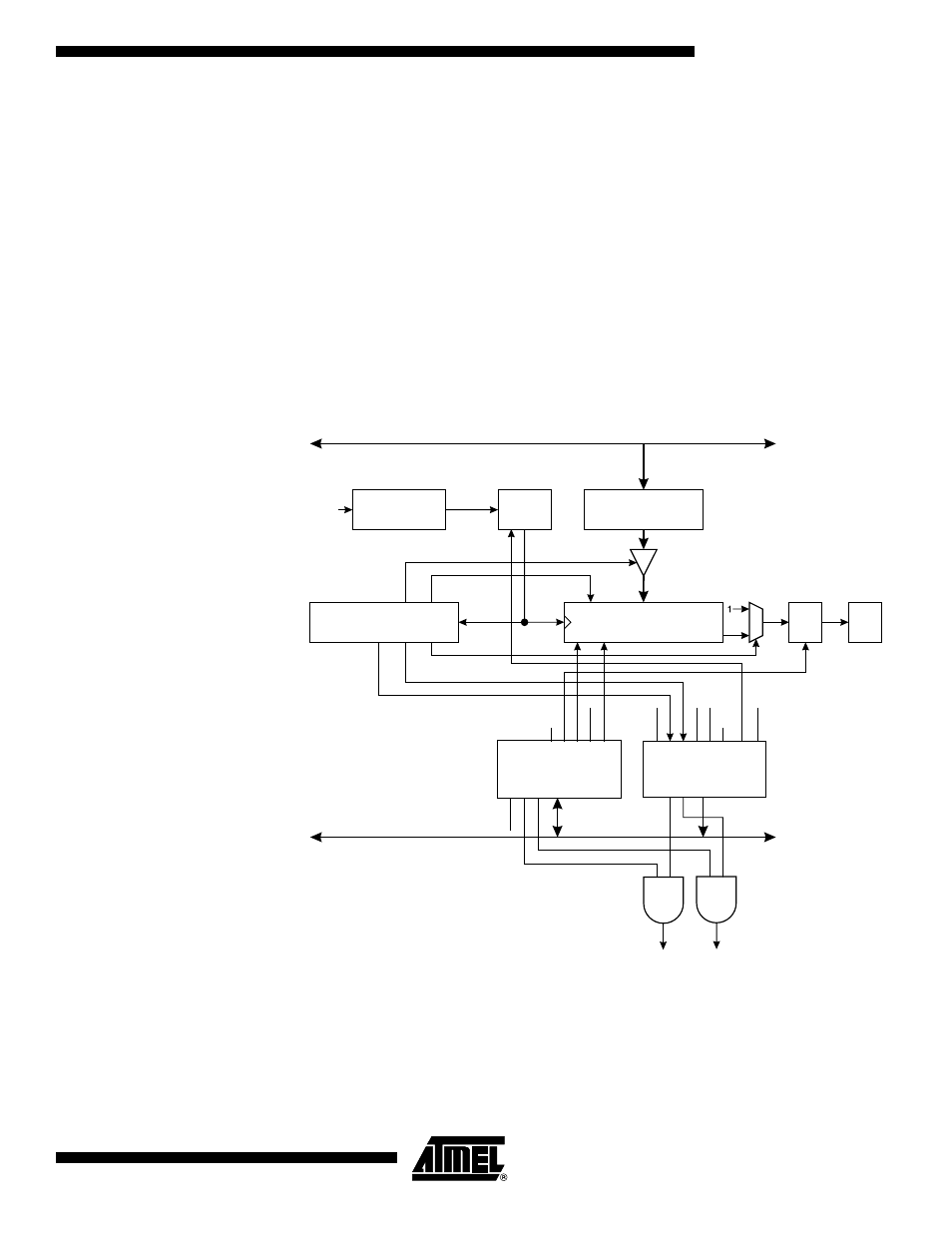

A block schematic of the UART Transmitter is shown in Figure 44. The two UARTs are

identical and the functionality is described in general for the two UARTs.

Figure 44. UART Transmitter

Data transmission is initiated by writing the data to be transmitted to the UART I/O Data

Register, UDRn. Data is transferred from UDRn to the Transmit Shift Register when:

•

A new character has been written to UDRn after the stop bit from the previous

character has been shifted out. The Shift Register is loaded immediately.

PD1/

PB3

U2Xn

10(11)-BIT TX

SHIFT REGISTER

PIN CONTROL

LOGIC

UART CONTROL AND

STATUS REGISTER

(UCSRnA)

UART CONTROL AND

STATUS REGISTER

(UCSRnB)

CONTROL LOGIC

BAUD RATE

GENERATOR

TXCn

IRQ

UDREn

IRQ

DATA BUS

RXCIEn

TXCIEn

UDRIEn

TXCn

UDREn

RXENn

TXENn

CHR9n

RXB8n

TXB8n

RXCn

TXCn

UDREn

FEn

MPCMPn

ORn

IDLE

BAUD

STORE UDRn

SHIFT ENABLE

DATA BUS

BAUD x 16

/16

UART I/O DATA

REGISTER (UDRn)

XTAL

TXDn

n = 0,1