Uart0 baud rate register low byte – ubrr0, Uart1 baud rate register low byte – ubrr1, Double-speed transmission – Rainbow Electronics ATmega161L User Manual

Page 78: Atmega161(l)

78

ATmega161(L)

1228C–AVR–08/02

UART0 and UART1 High Byte

Baud Rate Register UBRRHI

The UART Baud Register is a 12-bit register. The four most significant bits are located in

a separate register, UBRRHI. Note that both UART0 and UART1 share this register. Bit

7 to bit 4 of UBRRHI contain the four most significant bits of the UART1 Baud Register.

Bit 3 to bit 0 contain the four most significant bits of the UART0 Baud Register.

UART0 Baud Rate Register

Low Byte – UBRR0

UART1 Baud Rate Register

Low Byte – UBRR1

UBRRn stores the eight least significant bits of the UART Baud Rate Register.

Double-speed

Transmission

The ATmega161 provides a separate UART mode that allows the user to double the

communication speed. By setting the U2X bit in UART Control and Status Register

UCSRnA, the UART speed will be doubled. The data reception will differ slightly from

Normal mode. Since the speed is doubled, the Receiver front-end logic samples the sig-

nals on RXDn pin at a frequency 8 times the baud rate. While the line is idle, one single

sample of logical “0” will be interpreted as the falling edge of a start bit, and the start bit

detection sequence is initiated. Let sample 1 denote the first zero-sample. Following the

1-to-0 transition, the Receiver samples the RXDn pin at samples 4, 5 and 6. If two or

more of these three samples are found to be logical “1”s, the start bit is rejected as a

noise spike and the Receiver starts looking for the next 1-to-0 transition.

If, however, a valid start bit is detected, sampling of the data bits following the start bit is

performed. These bits are also sampled at samples 4, 5 and 6. The logical value found

in at least two of the three samples is taken as the bit value. All bits are shifted into the

Transmitter Shift Register as they are sampled. Sampling of an incoming character is

shown in Figure 47.

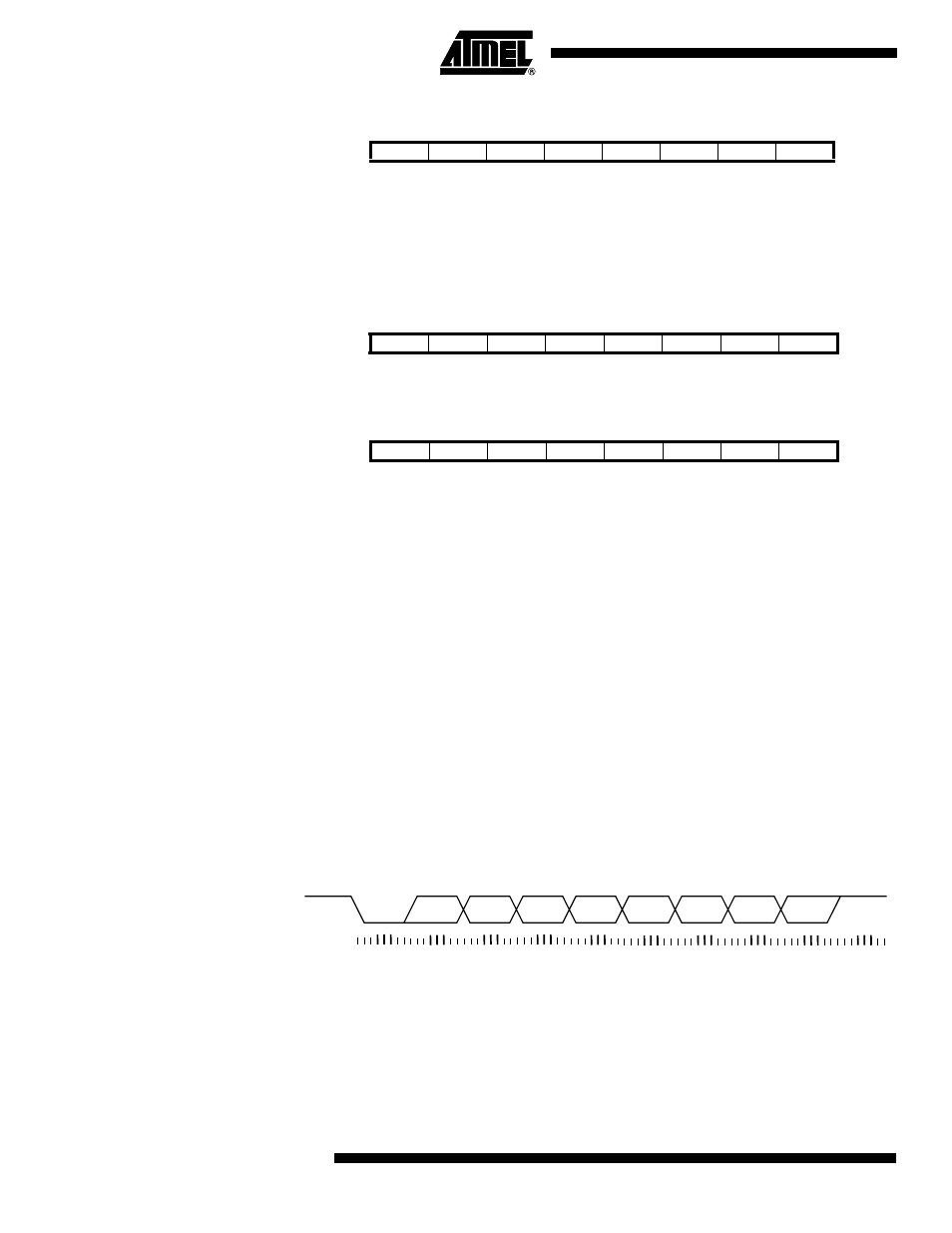

Figure 47. Sampling Received Data when the Transmission Speed is Doubled

Bit

7

6

5

4

3

2

1

0

$20 ($40)

MSB1

LSB1

MSB0

LSB0

UBRRHI

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$09 ($29)

MSB

LSB

UBRR0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$00 ($20)

MSB

LSB

UBRR1

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

START BIT

D0

D1

D2

D3

D4

D5

D6

D7

STOP BIT

RXD

RECEIVER

SAMPLING