Extended mcu control register – emcucr, Sleep modes, Idle mode – Rainbow Electronics ATmega161L User Manual

Page 36: Atmega161(l)

36

ATmega161(L)

1228C–AVR–08/02

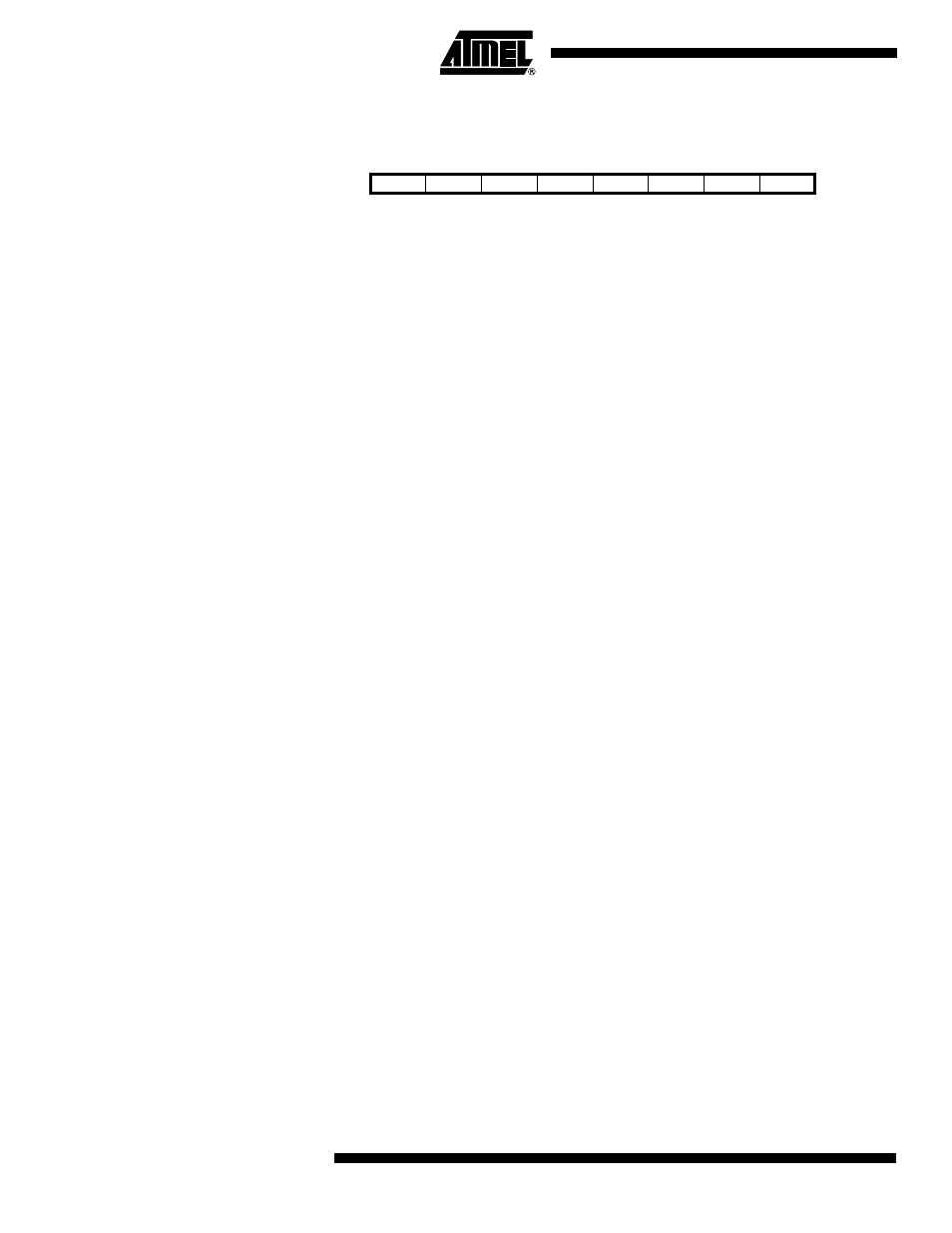

Extended MCU Control

Register – EMCUCR

The Extended MCU Control Register contains control bits for External Interrupt 2, Sleep

mode bit and control bits for the external memory interface.

• Bit 7

–

SM0: Sleep Mode Bit 0

When this bit is set (one) and Sleep mode bit 1 (SM1) in MCUCR is set, Power-save

mode is selected as Sleep mode. Refer to page 36 for a detailed description of the

Sleep modes.

• Bits 6..4

–

SRL2, SRL1, SRL0: External SRAM Limit

It is possible to configure different wait states for different external memory addresses in

ATmega161. The SRL2 - SRL0 bits are used to define at which address the different

wait states will be configured. See “Interface to External Memory” on page 84 for a

detailed description.

• Bits 3..1

–

SRW01, SRW00, SRW11: External SRAM Wait State Select Bits

The SRW01, SRW00 and SRW11 bits are used to set up extra wait states in the exter-

nal memory interface. See “Interface to External Memory” on page 84 for a detailed

description.

• Bit 0

–

ISC2: Interrupt Sense Control 2

The external interrupt 2 is activated by the external pin INT2 if the SREG I-Flag and the

corresponding interrupt mask in the GIMSK are set. If ISC2 is cleared (zero), a falling

edge on INT2 activates the interrupt. If ISC2 is set (one), a rising edge on INT2 activates

the interrupt. Edges on INT2 are registered asynchronously. Pulses on INT2 wider than

50 ns will generate an interrupt. Shorter pulses are not guaranteed to generate an

interrupt.

When changing the ISC2 bit, an interrupt can occur. Therefore, it is recommended to

first disable INT2 by clearing its Interrupt Enable bit in the GIMSK Register. Then, ISC2

bit can be changed. Finally, the INT2 Interrupt Flag should be cleared by writing a logical

“1” to its Interrupt Flag bit in the GIFR Register before the interrupt is re-enabled.

Sleep Modes

To enter any of the three Sleep modes, the SE bit in MCUCR must be set (one) and a

SLEEP instruction must be executed. The SM1 bit in the MCUCR Register and SM0 bit

in the EMCUCR Register select which Sleep mode (Idle, Power-down or Power-save)

will be activated by the SLEEP instruction (see Table 6). If an enabled interrupt occurs

while the MCU is in a Sleep mode, the MCU awakes. The CPU is then halted for four

cycles, it executes the interrupt routine, and resumes execution from the instruction fol-

lowing SLEEP. The contents of the Register File, SRAM and I/O memory are unaltered.

If a reset occurs during Sleep mode, the MCU wakes up and executes from the Reset

Vector.

Idle Mode

When the SM1/SM0 bits are set to 00, the SLEEP instruction makes the MCU enter the

Idle mo de, stoppi ng the CPU but allowing SPI, UARTs, Analog Com parato r,

Timer/Counters, Watchdog, and the Interrupt System to continue operating. This

enables the MCU to wake up from external triggered interrupts as well as internal ones

like the Timer Overflow and UART Receive Complete interrupts. If wake-up from the

Bit

7

6

5

4

3

2

1

0

$36 ($56)

SM0

SRL2

SRL1

SRL0

SRW01

SRW00

SRW11

ISC2

EMCUCR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0