Stack pointer – sp, Reset and interrupt handling, Atmega161(l) – Rainbow Electronics ATmega161L User Manual

Page 22: Bit 2

22

ATmega161(L)

1228C–AVR–08/02

• Bit 2

–

N: Negative Flag

The Negative Flag N indicates a negative result after the different arithmetic and logic

operations. See the Instruction Set description for detailed information.

• Bit 1

–

Z: Zero Flag

The Zero Flag Z indicates a zero result after the different arithmetic and logic opera-

tions. See the Instruction Set description for detailed information.

• Bit 0

–

C: Carry Flag

The Carry Flag C indicates a carry in an arithmetic or logic operation. See the Instruction

Set description for detailed information.

Note that the Status Register is not automatically stored when entering an interrupt rou-

tine and restored when returning from an interrupt routine. This must be handled by

software.

Stack Pointer – SP

The ATmega161 Stack Pointer is implemented as two 8-bit registers in the I/O space

locations $3E ($5E) and $3D ($5D). As the ATmega161 supports up to 64-Kbyte mem-

ory, all 16 bits are used.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Inter-

rupt Stacks are located. This Stack space in the data SRAM must be defined by the

program before any subroutine calls are executed or interrupts are enabled. The Stack

Pointer must be set to point above $60. The Stack Pointer is decremented by 1 when

data is pushed onto the Stack with the PUSH instruction, and it is decremented by 2

when an address is pushed onto the Stack with subroutine calls and interrupts. The

Stack Pointer is incremented by 1 when data is popped from the Stack with the POP

instruction, and it is incremented by 2 when an address is popped from the Stack with

return from subroutine RET or return from interrupt (RETI).

Reset and Interrupt

Handling

The ATmega161 provides 20 different interrupt sources. These interrupts and the sepa-

rate Reset Vector each have a separate Program Vector in the Program memory space.

All interrupts are assigned individual enable bits that must be set (one) together with the

I-bit in the Status Register in order to enable the interrupt.

The lowest addresses in the Program memory space are automatically defined as the

Reset and Interrupt vectors. The complete list of Vectors is shown in Table 2. The list

also determines the priority levels of the different interrupts. The lower the address, the

higher the priority level. RESET has the highest priority, and next is INT0 (the External

Interrupt Request 0) and so on.

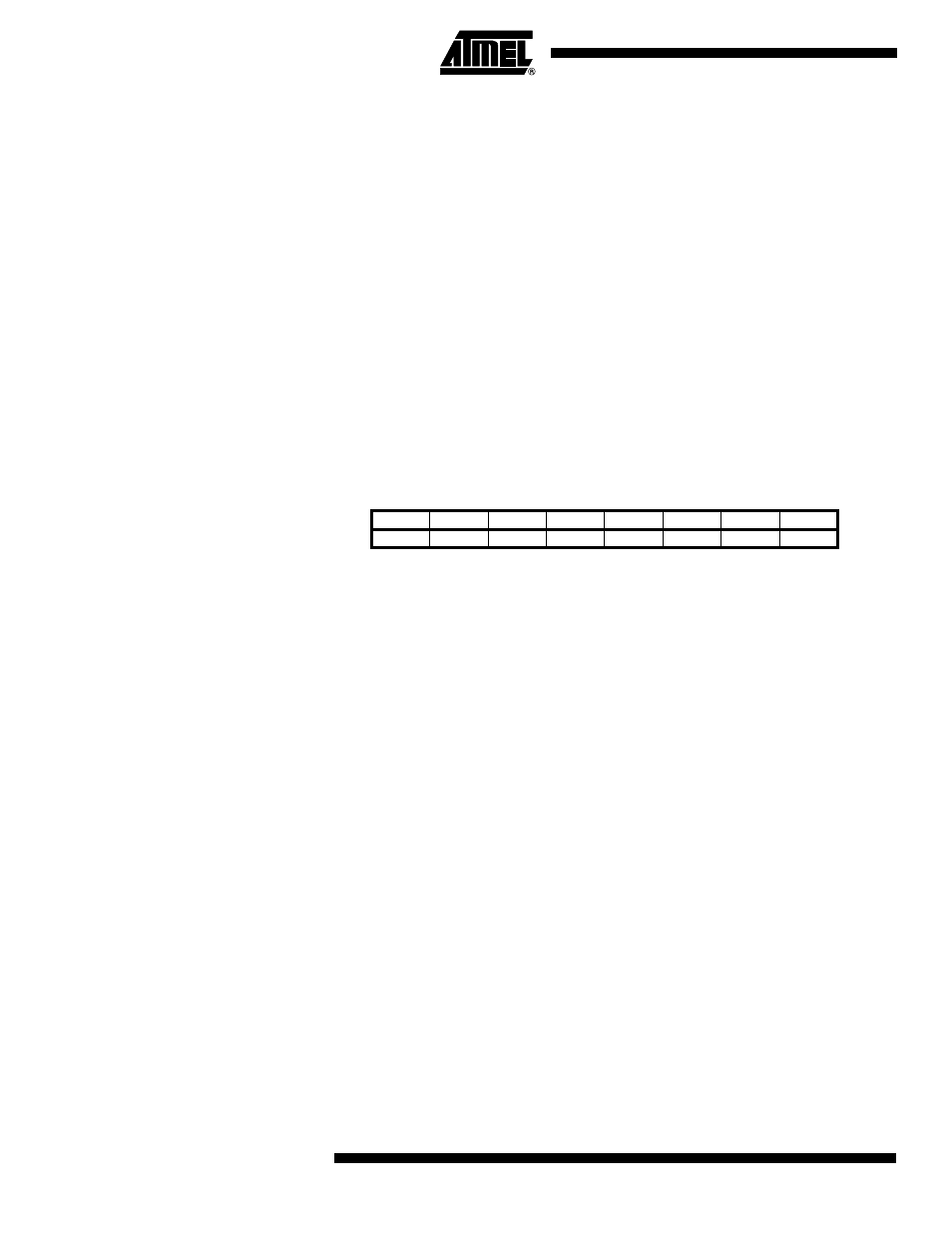

Bit

15

14

13

12

11

10

9

8

$3E ($5E)

SP15

SP14

SP13

SP12

SP11

SP10

SP9

SP8

SPH

$3D ($5D)

SP7

SP6

SP5

SP4

SP3

SP2

SP1

SP0

SPL

7

6

5

4

3

2

1

0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0