Ports as general digital i/o, Configuring the pin, Ports as general digital i/o” on – Rainbow Electronics ATmega128L User Manual

Page 61: Atmega128(l), Data bus, Sleep, and pud are common to all ports

61

ATmega128(L)

2467B–09/01

Ports as General Digital

I/O

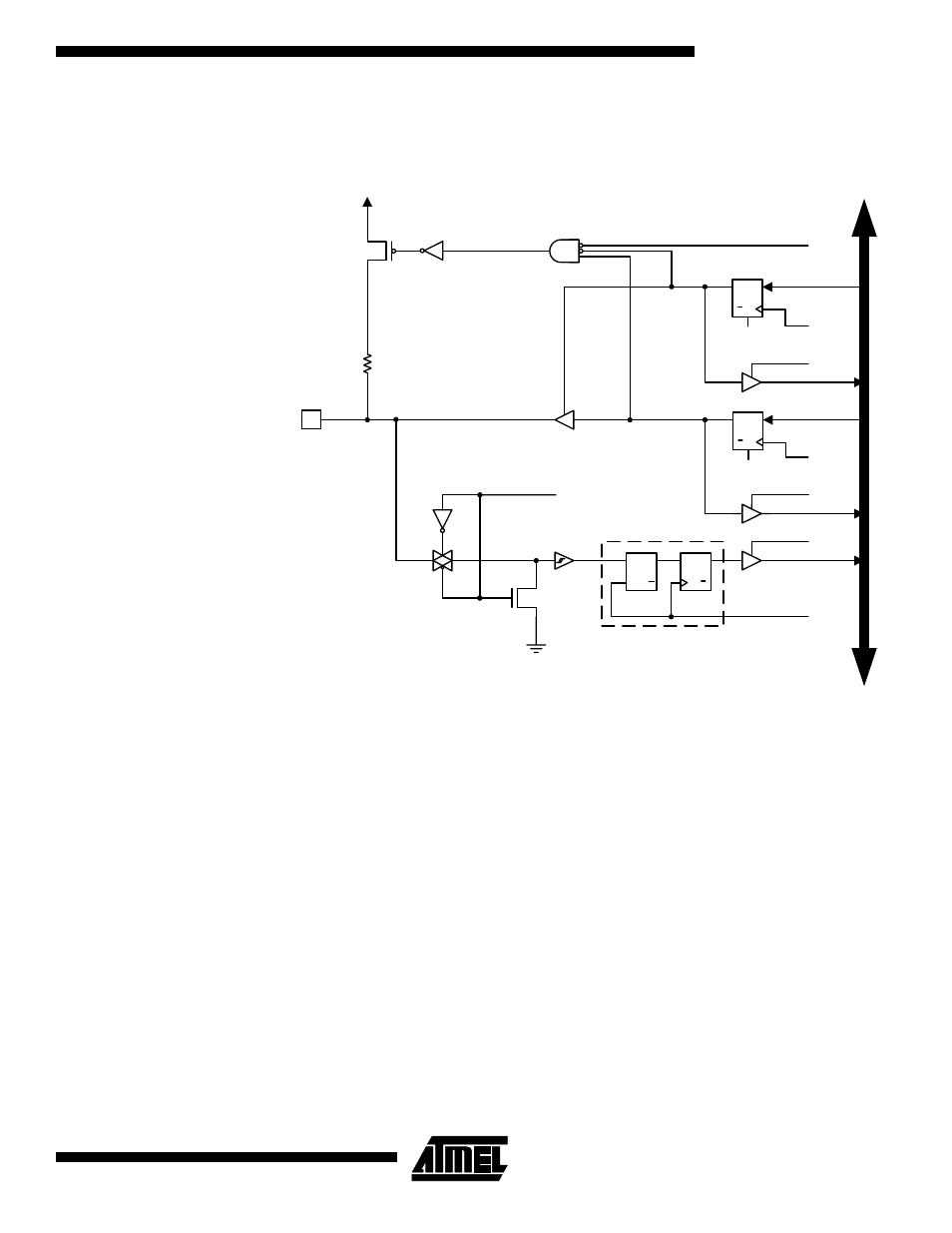

The ports are bi-directional I/O ports with optional internal pull-ups.

Figure 29 shows a

functional description of one I/O port pin, here generically called Pxn.

Figure 29. General Digital I/O

Note:

1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk

I/O

,

SLEEP, and PUD are common to all ports.

Configuring the Pin

Each port pin consists of 3 Register bits: DDxn, PORTxn, and PINxn. As shown in

ister Description for I/O Ports” on page 81, the DDxn bits are accessed at the DDRx I/O

address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O

address.

The DDxn bit in the DDRx register selects the direction of this pin. If DDxn is written

logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is config-

ured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up

resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic

zero or the pin has to be configured as an output pin. The port pins are tri-stated when a

reset condition becomes active, even if no clocks are running.

If PORTxn is written logic one when the pin is configured as an output pin, the port pin is

driven high (one). If PORTxn is written logic zero when the pin is configured as an out-

put pin, the port pin is driven low (zero).

clk

RPx

RRx

WPx

RDx

WDx

PUD

SYNCHRONIZER

WDx:

WRITE DDRx

WPx:

WRITE PORTx

RRx:

READ PORTx REGISTER

RPx:

READ PORTx PIN

PUD:

PULLUP DISABLE

clk

I/O

:

I/O CLOCK

RDx:

READ DDRx

D

L

Q

Q

RESET

RESET

Q

Q

D

Q

Q

D

CLR

PORTxn

Q

Q

D

CLR

DDxn

PINxn

DATA BUS

SLEEP

SLEEP:

SLEEP CONTROL

Pxn

I/O