Atmega128(l) – Rainbow Electronics ATmega128L User Manual

Page 318

318

ATmega128(L)

2467B–09/01

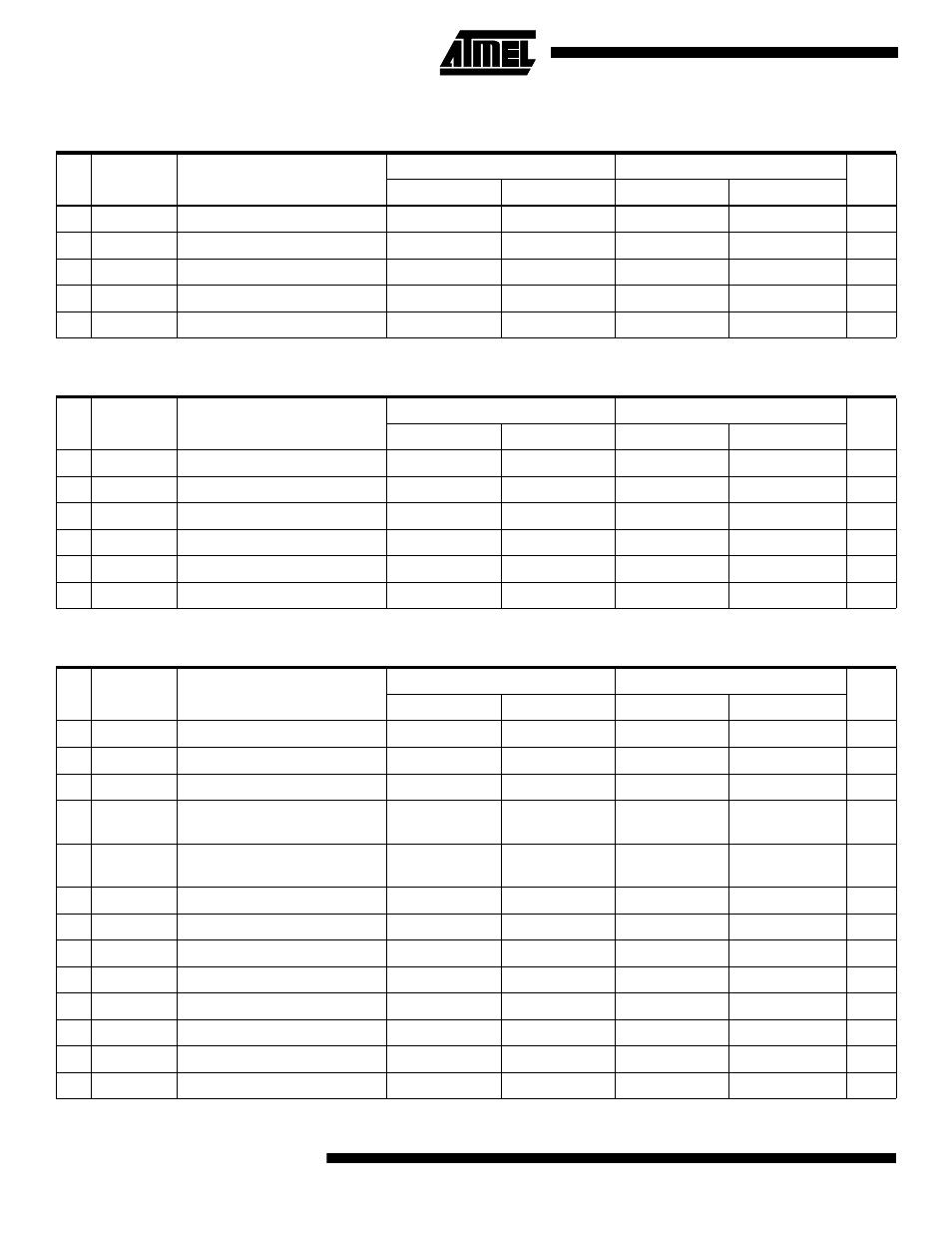

Table 140. External Data Memory Characteristics, 4.5 - 5.5 Volts, SRWn1 = 1, SRWn0 = 0

Symbol

Parameter

4 MHz Oscillator

Variable Oscillator

Unit

Min

Max

Min

Max

0

1/t

CLCL

Oscillator Frequency

0.0

TBD

MHz

10

t

RLDV

Read Low to Data Valid

TBD

3.0t

CLCL

-TBD

ns

12

t

RLRH

RD Pulse Width

TBD

3.0t

CLCL

-TBD

ns

15

t

DVWH

Data Valid to WR High

TBD

3.0t

CLCL

-TBD

ns

16

t

WLWH

WR Pulse Width

TBD

3.0t

CLCL

-TBD

ns

Table 141. External Data Memory Characteristics, 4.5 - 5.5 Volts, SRWn1 = 1, SRWn0 = 1

Symbol

Parameter

4 MHz Oscillator

Variable Oscillator

Unit

Min

Max

Min

Max

0

1/t

CLCL

Oscillator Frequency

0.0

TBD

MHz

10

t

RLDV

Read Low to Data Valid

TBD

3.0t

CLCL

-TBD

ns

12

t

RLRH

RD Pulse Width

TBD

3.0t

CLCL

-TBD

ns

14

t

WHDX

Data Hold After WR High

TBD

1.5t

CLCL

-TBD

ns

15

t

DVWH

Data Valid to WR High

TBD

3.0t

CLCL

-TBD

ns

16

t

WLWH

WR Pulse Width

TBD

3.0t

CLCL

-TBD

ns

Table 142. External Data Memory Characteristics, 2.7 - 5.5 Volts, No Wait-state

Symbol

Parameter

4 MHz Oscillator

Variable Oscillator

Unit

Min

Max

Min

Max

0

1/t

CLCL

Oscillator Frequency

0.0

TBD

MHz

1

t

LHLL

ALE Pulse Width

TBD

t

CLCL

-TBD

ns

2

t

AVLL

Address Valid A to ALE Low

TBD

0.5t

CLCL

-TBD

ns

3a

t

LLAX_ST

Address Hold After ALE Low,

write access

TBD

TBD

ns

3b

t

LLAX_LD

Address Hold after ALE Low,

read access

TBD

TBD

ns

4

t

AVLLC

Address Valid C to ALE Low

TBD

0.5t

CLCL

-TBD

ns

5

t

AVRL

Address Valid to RD Low

TBD

1.0t

CLCL

-TBD

ns

6

t

AVWL

Address Valid to WR Low

TBD

1.0t

CLCL

-TBD

ns

7

t

LLWL

ALE Low to WR Low

TBD

TBD

0.5t

CLCL

-TBD

0.5t

CLCL

-TBD

ns

8

t

LLRL

ALE Low to RD Low

TBD

TBD

0.5t

CLCL

-TBD

0.5t

CLCL

-TBD

ns

9

t

DVRH

Data Setup to RD High

TBD

TBD

ns

10

t

RLDV

Read Low to Data Valid

TBD

TBD

ns

11

t

RHDX

Data Hold After RD High

TBD

TBD

ns