Table 104, Atmega128(l) – Rainbow Electronics ATmega128L User Manual

Page 254

254

ATmega128(L)

2467B–09/01

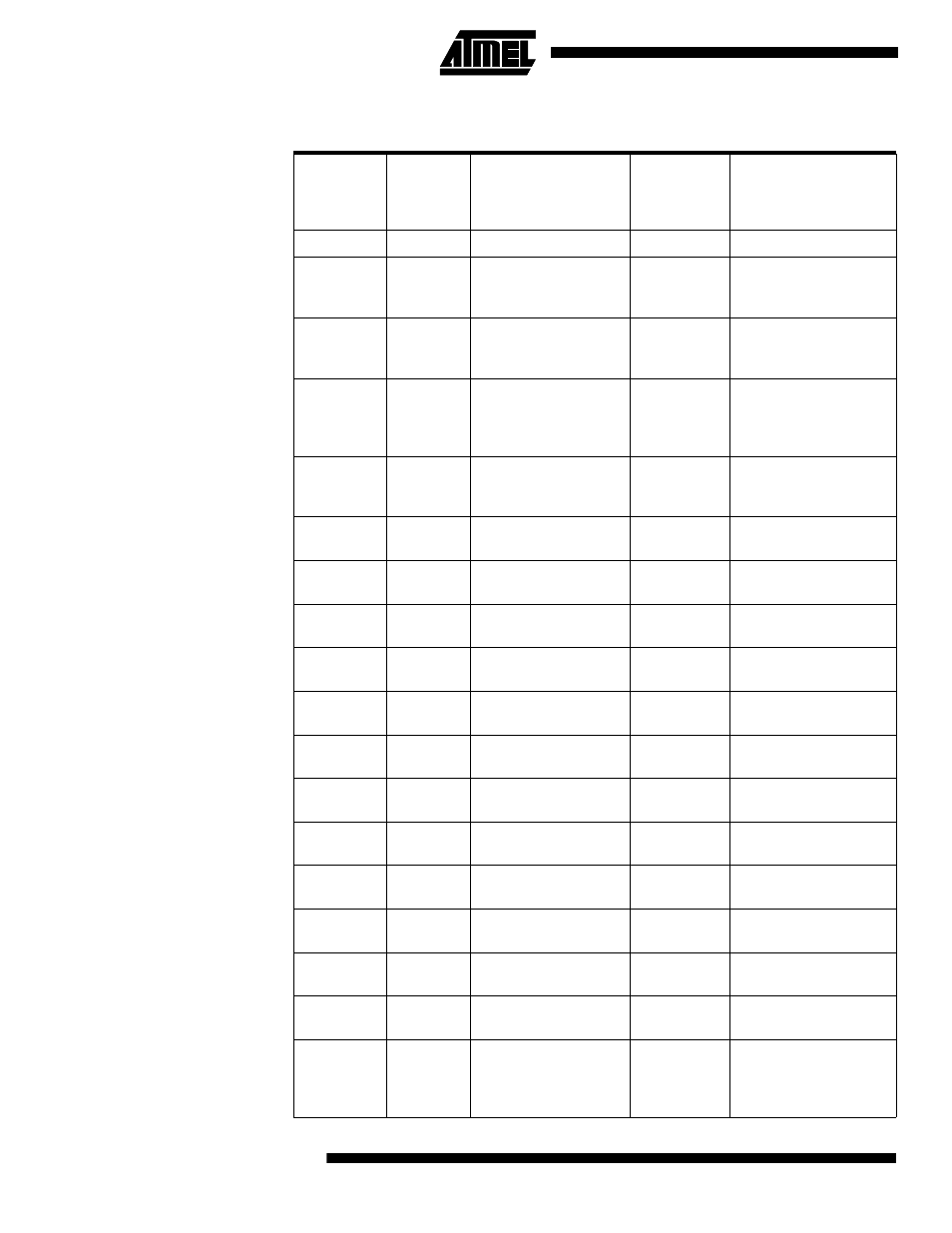

Table 104. Boundary-scan Signals for the ADC

Signal

Name

Direction

as Seen

from the

ADC

Description

Recommen-

ded Input

when not

in Use

Output Values when

Recommended Inputs

are Used, and CPU is

not Using the ADC

COMP

Output

Comparator Output

0

0

ACLK

Input

Clock signal to gain

stages implemented

as Switch-Cap filters

0

0

ACTEN

Input

Enable path from gain

stages to the

comparator

0

0

ADHSM

Input

Increases speed of

comparator at the

sacrifice of higher

power consumption

0

0

ADCBGEN

Input

Enable Band-gap

reference as negative

input to comparator

0

0

ADCEN

Input

Power-On signal to the

ADC

0

0

AMPEN

Input

Power-On signal to the

gain stages

0

0

DAC_9

Input

Bit 9 of digital value to

DAC

1

1

DAC_8

Input

Bit 8 of digital value to

DAC

0

0

DAC_7

Input

Bit 7 of digital value to

DAC

0

0

DAC_6

Input

Bit 6 of digital value to

DAC

0

0

DAC_5

Input

Bit 5 of digital value to

DAC

0

0

DAC_4

Input

Bit 4 of digital value to

DAC

0

0

DAC_3

Input

Bit 3 of digital value to

DAC

0

0

DAC_2

Input

Bit 2 of digital value to

DAC

0

0

DAC_1

Input

Bit 1 of digital value to

DAC

0

0

DAC_0

Input

Bit 0 of digital value to

DAC

0

0

EXTCH

Input

Connect ADC

channels 0-3 to by-

pass path around gain

stages

1

1