Modes of operation, Normal mode, Clear timer on compare match (ctc) mode – Rainbow Electronics ATmega128L User Manual

Page 145: Atmega128(l)

145

ATmega128(L)

2467B–09/01

A change of the COM21:0 bits state will have effect at the first compare match after the

bits are written. For non-PWM modes, the action can be forced to have immediate effect

by using the FOC2 strobe bits.

Modes of Operation

The mode of operation, i.e. the behavior of the Timer/Counter and the output compare

pins, is defined by the combination of the waveform generation mode (WGM21:0) and

compare output mode (COM21:0) bits. The compare output mode bits do not affect the

counting sequence, while the waveform generation mode bits do. The COM21:0 bits

control whether the PWM output generated should be inverted or not (inverted or non-

inverted PWM). For non-PWM modes the COM21:0 bits control whether the output

should be set, cleared, or toggled at a compare match (

For detailed timing information refer to

Figure 67, Figure 68, Figure 69, and Figure 70 in

“Timer/Counter Timing Diagrams” on page 149.

Normal Mode

The simplest mode of operation is the normal mode (WGM21:0 = 0). In this mode the

counting direction is always up (incrementing), and no counter clear is performed. The

counter simply overruns when it passes its maximum 8-bit value (TOP = 0xFF) and then

restarts from the bottom (0x00). In normal operation the Timer/Counter overflow flag

(

TOV

2) will be set in the same timer clock cycle as the TCNT2 becomes zero. The

TOV

2

flag in this case behaves like a 9th bit, except that it is only set, not cleared. However,

combined with the timer overflow interrupt that automatically clears the

TOV

2 flag, the

timer resolution can be increased by software. There are no special cases to consider in

the normal mode, a new counter value can be written anytime.

The output compare unit can be used to generate interrupts at some given time. Using

the output compare to generate waveforms in normal mode is not recommended, since

this will occupy too much of the CPU time.

Clear Timer on Compare

Match (CTC) Mode

In clear timer on compare or CTC mode (WGM21:0 = 2), the OCR2 register is used to

manipulate the counter resolution. In CTC mode the counter is cleared to zero when the

counter value (TCNT2) matches the OCR2. The OCR2 defines the top value for the

counter, hence also its resolution. This mode allows greater control of the compare

match output frequency. It also simplifies the operation of counting external events.

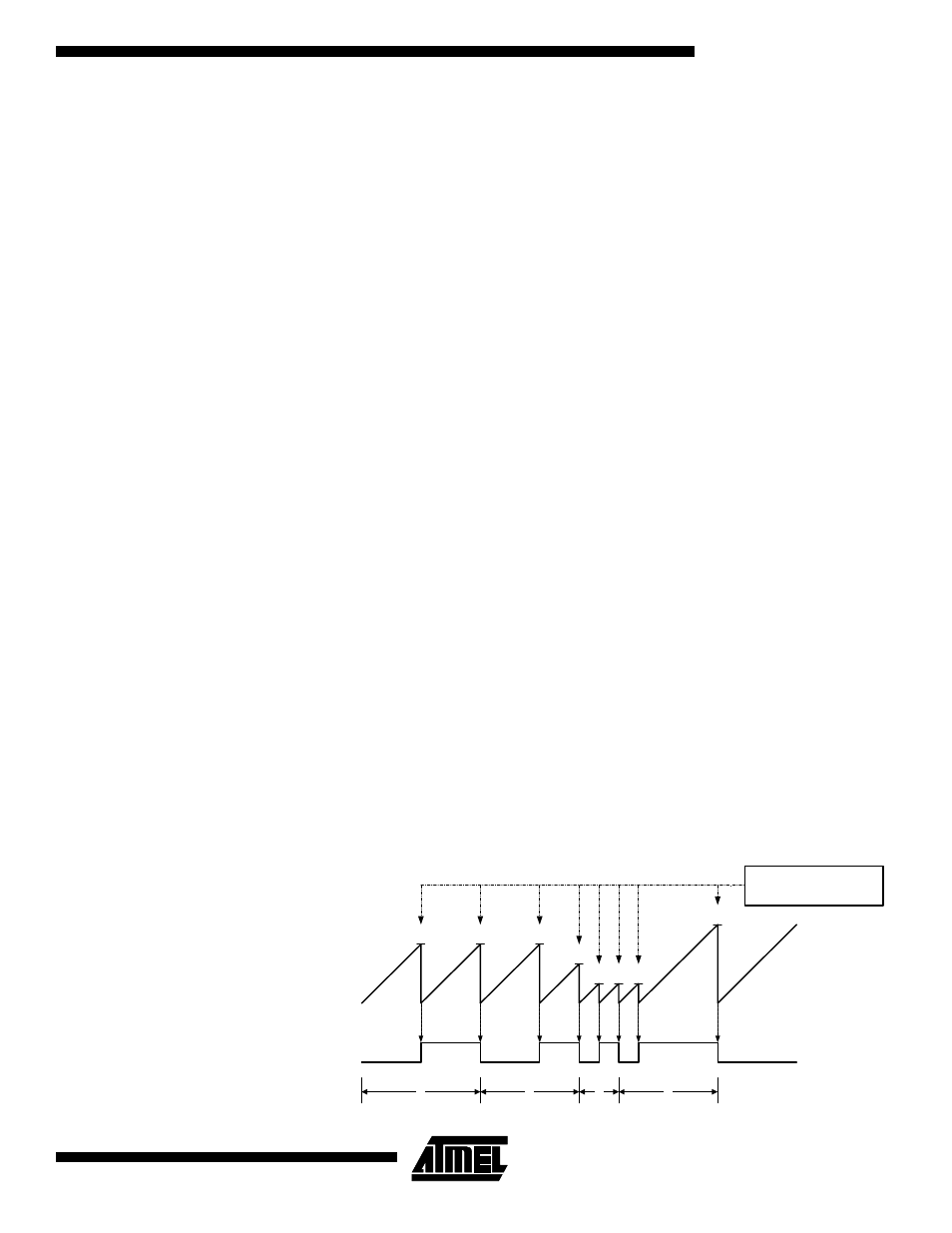

The timing diagram for the CTC mode is shown in

Figure 64. The counter value

(TCNT2) increases until a compare match occurs between TCNT2 and OCR2 and then

counter (TCNT2) is cleared.

Figure 64. CTC Mode, Timing Diagram

TCNTn

OCn

(Toggle)

OCn Interrupt Flag Set

1

4

Period

2

3

(COMn1:0 = 1)