Timer/counter 3 control register c – tccr3c, Timer/counter 1 – tcnt1h and tcnt1l, Timer/counter 3 – tcnt3h and tcnt3l – Rainbow Electronics ATmega128L User Manual

Page 132: Atmega128(l)

132

ATmega128(L)

2467B–09/01

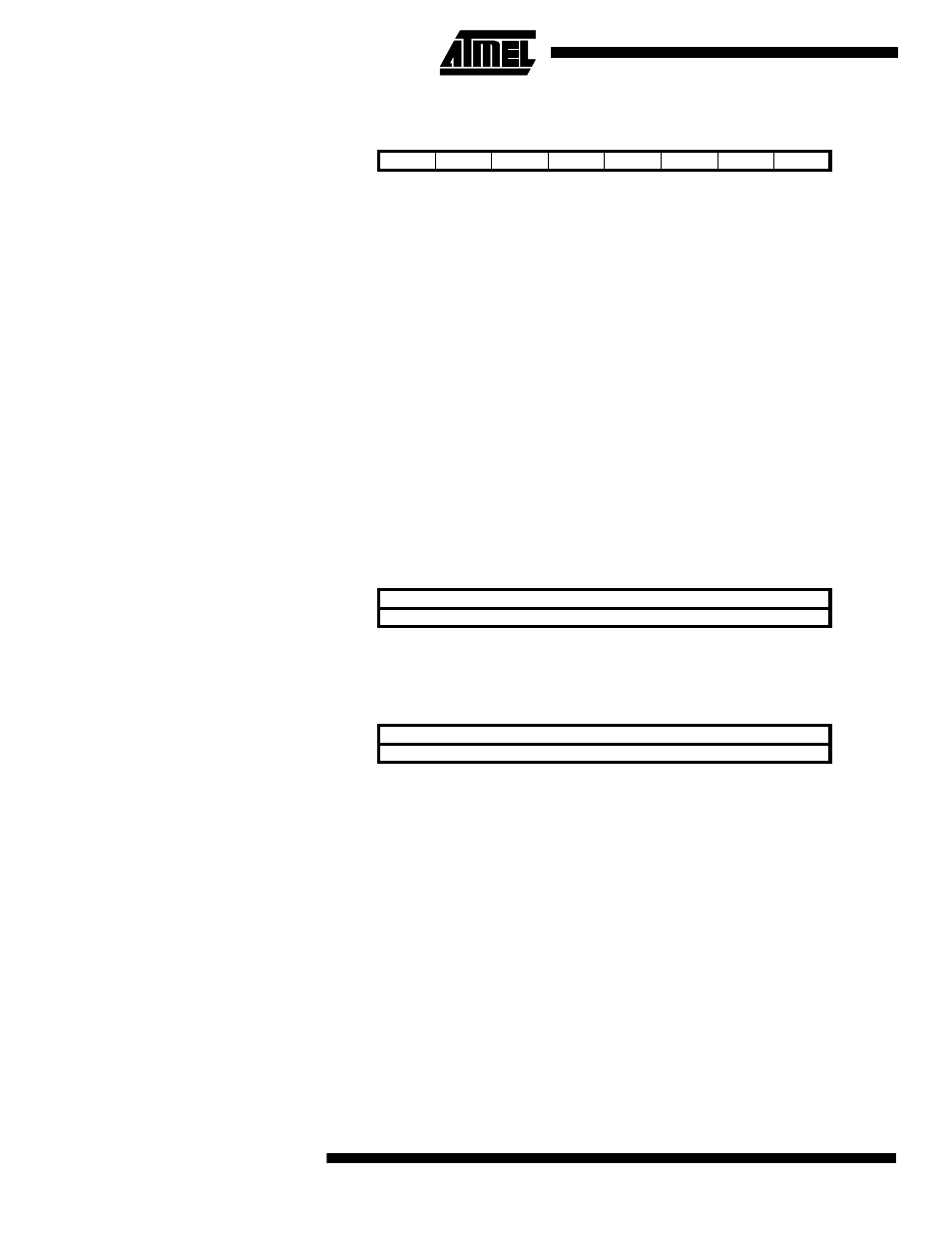

Timer/Counter 3 Control

Register C – TCCR3C

•

Bit 7- FOCnA: Force Output Compare for Channel A

•

Bit 6- FOCnB: Force Output Compare for Channel B

•

Bit 5- FOCnC: Force Output Compare for Channel C

The FOCnA/FOCnB/FOCnC bits are only active when the WGMn3:0 bits specifies a

non-PWM mode. When writing a logical one to the FOCnA/FOCnB/FOCnC bit, an

im med iate comp are m atch is force d o n th e wa ve form g enerat ion unit. Th e

OCnA/OCnB/OCnC output is changed according to its COMnx1:0 bits setting. Note that

the FOCnA/FOCnB/FOCnC bits are implemented as strobes. Therefore it is the value

present in the COMnx1:0 bits that determine the effect of the forced compare.

A FOCnA/FOCnB/FOCnC strobe will not generate any interrupt nor will it clear the timer

in clear timer on compare match (CTC) mode using OCRnA as TOP.

The FOCnA/FOCnB/FOCnB bits are always read as zero.

•

Bit 4:0 - Reserved Bits

These bits are reserved for future use. For ensuring compatibility with future devices,

these bits must be written to zero when TCCRnC is written.

Timer/Counter 1 – TCNT1H

and TCNT1L

Timer/Counter 3 – TCNT3H

and TCNT3L

The two Timer/Counter I/O locations (TCNTnH and TCNTnL, combined TCNTn) give

direct access, both for read and for write operations, to the Timer/Counter unit 16-bit

counter. To ensure that both the high and low bytes are read and written simultaneously

when the CPU accesses these registers, the access is performed using an 8-bit tempo-

rary high byte register (TEMP). This temporary register is shared by all the other 16-bit

registers.

See “Accessing 16-bit Registers” on page 109.

Modifying the counter (TCNTn) while the counter is running introduces a risk of missing

a compare match between TCNTn and one of the OCRnx registers.

Writing to the TCNTn register blocks (removes) the compare match on the following

timer clock for all compare units.

Bit

7

6

5

4

3

2

1

0

FOC3A

FOC3B

FOC3C

–

–

–

–

–

TCCR3C

Read/Write

W

W

W

R

R

R

R

R

Initial value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

TCNT1[15:8]

TCNT1H

TCNT1[7:0]

TCNT1L

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

TCNT3[15:8]

TCNT3H

TCNT3[7:0]

TCNT3L

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0