Timer/counter interrupt flag register – tifr, Atmega162/v – Rainbow Electronics ATmega162V User Manual

Page 155

155

ATmega162/V

2513E–AVR–09/03

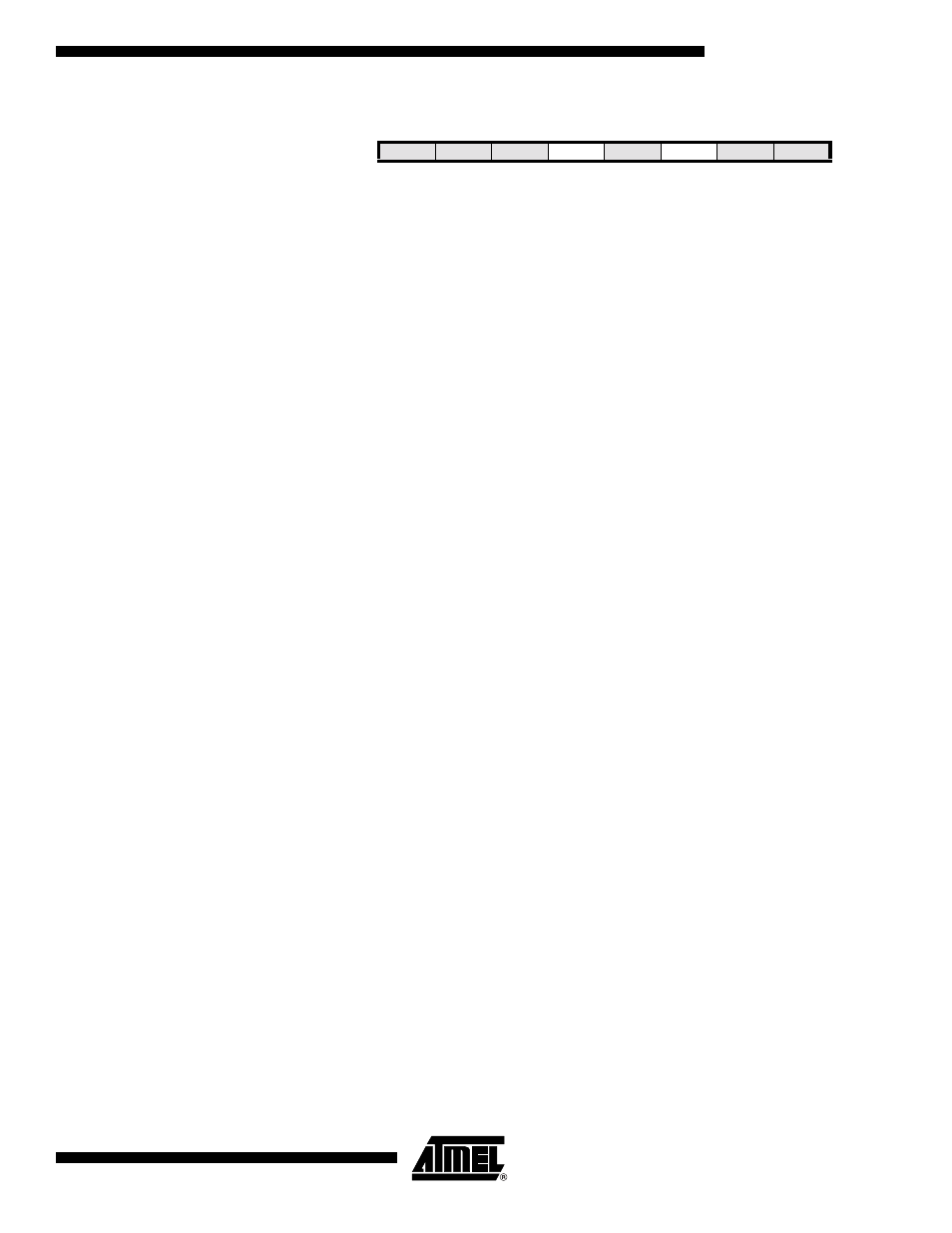

Timer/Counter Interrupt Flag

Register – TIFR

• Bit 4 – OCF2: Output Compare Flag 2

The OCF2 bit is set (one) when a Compare Match occurs between the Timer/Counter2

and the data in OCR2 – Output Compare Register2. OCF2 is cleared by hardware when

executing the corresponding interrupt handling vector. Alternatively, OCF2 is cleared by

writing a logic one to the flag. When the I-bit in SREG, OCIE2 (Timer/Counter2 Com-

pare Match Interrupt Enable), and OCF2 are set (one), the Timer/Counter2 Compare

Match Interrupt is executed.

• Bit 2 – TOV2: Timer/Counter2 Overflow Flag

The TOV2 bit is set (one) when an overflow occurs in Timer/Counter2. TOV2 is cleared

by hardware when executing the corresponding interrupt handling vector. Alternatively,

TOV2 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE2

(T im er/C o un ter 2 O ve rflo w In ter rup t En ab le ), a n d TO V 2 a re s et (o ne ), the

Timer/Counter2 Overflow interrupt is executed. In PWM mode, this bit is set when

Timer/Counter2 changes counting direction at 0x00.

Bit

7

6

5

4

3

2

1

0

TOV1

OCF1A

OC1FB

OCF2

ICF1

TOV2

TOV0

OCF0

TIFR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial Value

0

0

0

0

0

0

0

0