Uart control register - ucr – Rainbow Electronics ATmega103L User Manual

Page 63

ATmega603/103

63

When the TXCIE bit in UCR is set, setting of TXC causes the UART Transmit Complete interrupt to be executed. TXC is

cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, the TXC bit is cleared

(zero) by writing a logical one to the bit.

•

Bit 5 - UDRE: UART Data Register Empty

This bit is set (one) when a character written to UDR is transferred to the Transmit shift register. Setting of this bit indicates

that the transmitter is ready to receive a new character for transmission.

When the UDRIE bit in UCR is set, the UART Transmit Complete interrupt to be executed as long as UDRE is set. UDRE is

cleared by writing UDR. When interrupt-driven data transmittal is used, the UART Data Register Empty Interrupt routine

must write UDR in order to clear UDRE, otherwise a new interrupt will occur once the interrupt routine terminates.

UDRE is set (one) during reset to indicate that the transmitter is ready.

•

Bit 4 - FE: Framing Error

This bit is set if a Framing Error condition is detected, i.e. when the stop bit of an incoming character is zero.

The FE bit is cleared when the stop bit of received data is one.

•

Bit 3 - OR: OverRun

This bit is set if an Overrun condition is detected, i.e. when a character already present in the UDR register is not read

before the next character is transferred from the Receiver Shift register. The OR bit is buffered, which means that it is will

be set once the valid data still in UDRE is read.

The OR bit is cleared (zero) when data is received and transferred to UDR.

•

Bits 2..0 - Res: Reserved bits

These bits are reserved bits in the ATmega603/103 and will always read as zero.

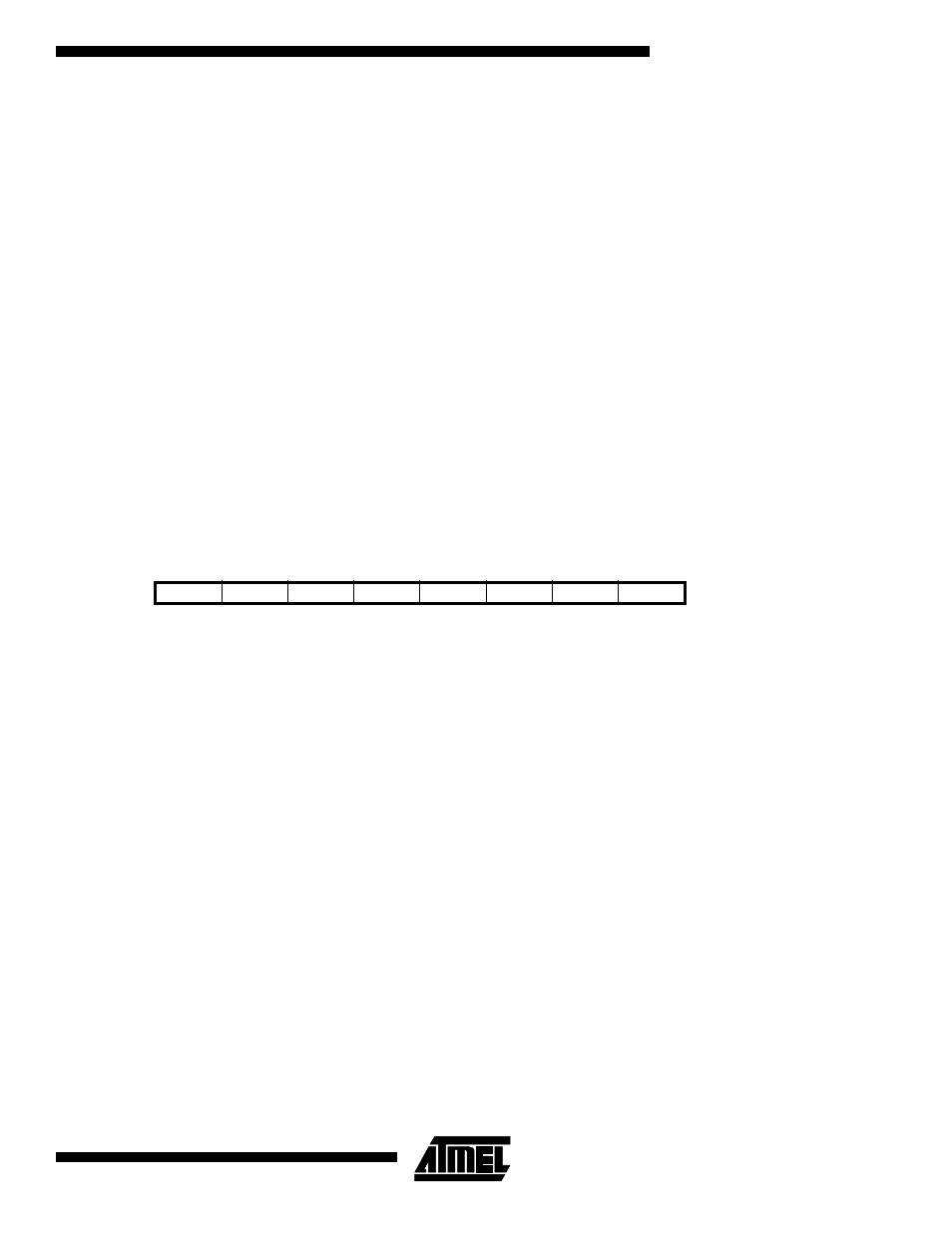

UART Control Register - UCR

•

Bit 7 - RXCIE: RX Complete Interrupt Enable

When this bit is set (one), a setting of the RXC bit in USR will cause the Receive Complete interrupt routine to be executed

provided that global interrupts are enabled.

•

Bit 6 - TXCIE: TX Complete Interrupt Enable

When this bit is set (one), a setting of the TXC bit in USR will cause the Transmit Complete interrupt routine to be executed

provided that global interrupts are enabled.

•

Bit 5 - UDRIE: UART Data Register Empty Interrupt Enable

When this bit is set (one), a setting of the UDRE bit in USR will cause the UART Data Register Empty interrupt routine to be

executed provided that global interrupts are enabled.

•

Bit 4 - RXEN: Receiver Enable

This bit enables the UART receiver when set (one). When the receiver is disabled, the TXC, OR and FE status flags cannot

become set. If these flags are set, turning off RXEN does not cause them to be cleared.

•

Bit 3 - TXEN: Transmitter Enable

This bit enables the UART transmitter when set (one). When disabling the transmitter while transmitting a character, the

transmitter is not disabled before the character in the shift register plus any following character in UDR has been com-

pletely transmitted.

•

Bit 2 - CHR9: 9 Bit Characters

When this bit is set (one) transmitted and received characters are 9 bit long plus start and stop bits. The 9th bit is read and

written by using the RXB8 and TXB8 bits in UCR, respectively. The 9th data bit can be used as an extra stop bit or a parity

bit.

•

Bit 1 - RXB8: Receive Data Bit 8

When CHR9 is set (one), RXB8 is the 9th data bit of the received character.

Bit

7

6

5

4

3

2

1

0

$0A ($2A)

RXCIE

TXCIE

UDRIE

RXEN

TXEN

CHR9

RXB8

TXB8

UCR

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R

W

Initial value

0

0

0

0

0

0

1

0