Xtal divide control register - xdiv – Rainbow Electronics ATmega103L User Manual

Page 23

ATmega603/103

23

•

Bits 4,3 - SM1/SM0: Sleep Mode Select bits 1 and 0

This bit selects between the three available sleep modes as shown in the following table:

•

Bits 2..0 - Res: Reserved bits

These bits are reserved bits in the ATmega603/103 and always read zero.

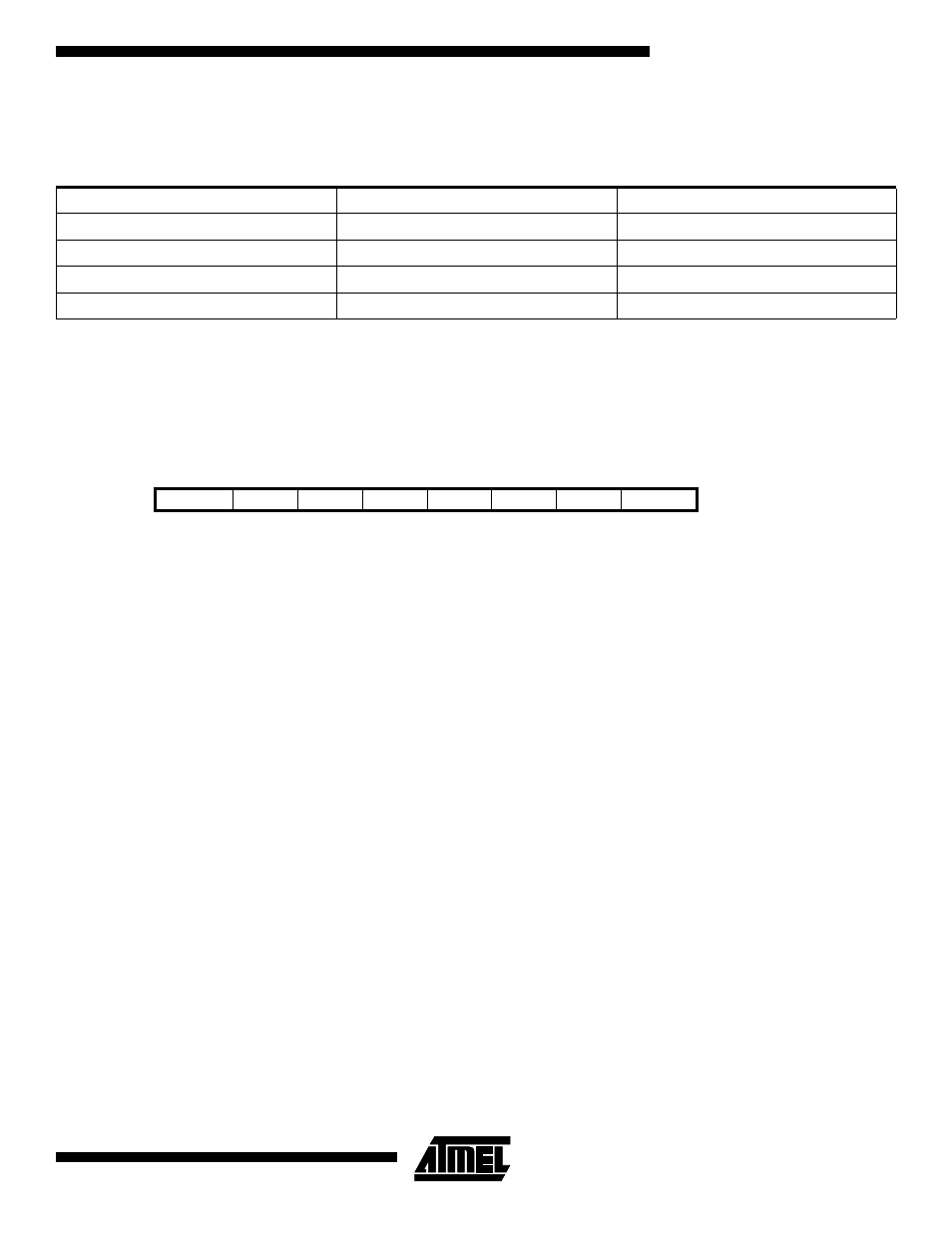

XTAL Divide Control Register - XDIV

The XTAL Divide Control Register is used to divide the XTAL clock frequency by a number in the range 1 - 129. This fea-

ture can be used to decrease power consumption when the requirement for processing power is low.

•

Bit 7 - XDIVEN: XTAL Divide Enable

When the XDIVEN bit is set (one), the clock frequency of the CPU and all peripherals is divided by the factor defined by the

setting of XDIV6 - XDIV0. This bit can be set and cleared run-time to vary the clock frequency as suitable to the application.

•

Bits 6..0 - XDIV6..XDIV0: XTAL Divide Select Bits 6 - 0

These bits define the division factor that applies when the XDIVEN bit is set (one). If the value of these bits is denoted

d,

the following formula defines the resulting CPU clock frequency

f

clk

:

The value of these bits can only be changed when XDIVEN is zero. When XDIVEN is set to one, the value written simulta-

neously into XDIV6..XDIV0 is taken as the division factor. When XDIVEN is cleared to zero, the value written

simultaneously into XDIV6..XDIV0 is rejected. As the divider divides the master clock input to the MCU, the speed of all

peripherals is reduced when a division factor is used.

Table 4. Sleep Mode Select

SM1

SM0

Sleep Mode

0

0

Idle Mode

0

1

Reserved

1

0

Power Down

1

1

Power Save

Bit

7

6

5

4

3

2

1

0

$3C ($5C)

XDIVEN

XDIV6

XDIV5

XDIV4

XDIV3

XDIV2

XDIV1

XDIV0

XDIV

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

f

CLK

XTAL

129

d

–

-------------------

=