Timer/counter0 - tcnt0, Timer/counter2 - tcnt2 – Rainbow Electronics ATmega103L User Manual

Page 39

ATmega603/103

39

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK

CPU clock. If the external pin modes are used for Timer/Counter2, transitions on PD7/(T2) will clock the counter even if the

pin is configured as an output. This feature can give the user SW control of the counting.

Timer/Counter0 - TCNT0

Timer/Counter2 - TCNT2

These 8-bit registers contains the value of the Timer/Counters.

Both Timer/Counters are realized as up or up/down (in PWM mode) counters with read and write access. If the

Timer/Counter is written to and a clock source is selected, it continues counting in the timer clock cycle after it is preset with

the written value.

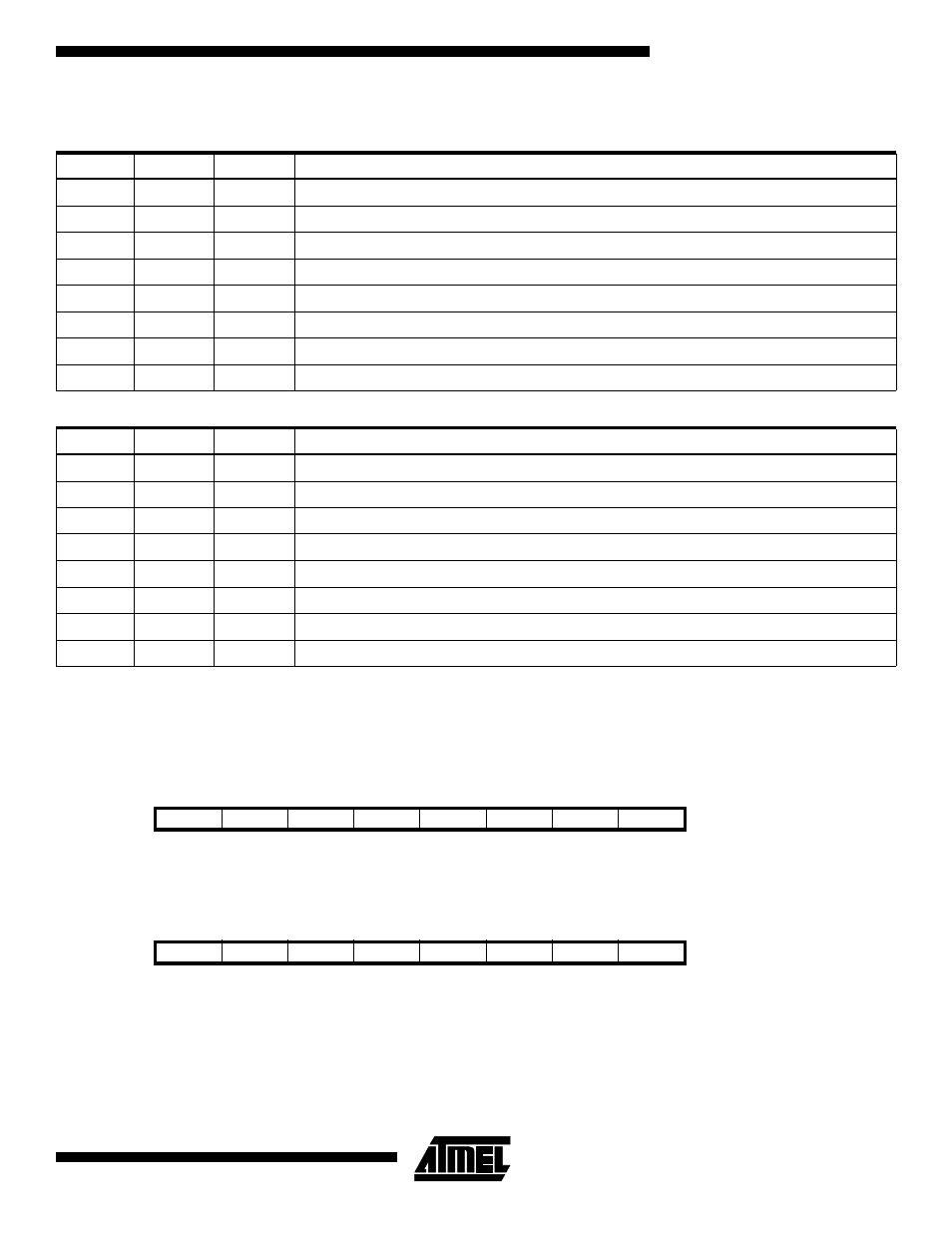

Table 12. Timer/Counter0 Prescale Select

CS02

CS01

CS00

Description

0

0

0

Timer/Counter0 is stopped.

0

0

1

PCK0

0

1

0

PCK0/8

0

1

1

PCK0/32

1

0

0

PCK0/64

1

0

1

PCK0/128

1

1

0

PCK0/256

1

1

1

PCK0/1024

Table 13. Timer/Counter2 Prescale Select

CS22

CS21

CS20

Description

0

0

0

Timer/Counter2 is stopped.

0

0

1

CK

0

1

0

CK/8

0

1

1

CK/64

1

0

0

CK/256

1

0

1

CK/1024

1

1

0

External Pin PD7(T2), falling edge

1

1

1

External Pin PD7(T2), rising edge

Bit

7

6

5

4

3

2

1

0

$32 ($42)

MSB

LSB

TCNT0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0

Bit

7

6

5

4

3

2

1

0

$24 ($44)

MSB

LSB

TCNT2

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value

0

0

0

0

0

0

0

0