Mcu control register - mcucr – Rainbow Electronics ATmega103L User Manual

Page 22

ATmega603/103

22

The Stack Pointer points to the data SRAM stack area where the Subroutine and Interrupt Stacks are located. This Stack

space in the data SRAM must be defined by the program before any subroutine calls are executed or interrupts are

enabled. The stack pointer must be set to point above $60. The Stack Pointer is decremented by one when data is pushed

onto the Stack with the PUSH instruction, and it is decremented by two when an address is pushed onto the Stack with

subroutine calls and interrupts. The Stack Pointer is incremented by one when data is popped from the Stack with the POP

instruction, and it is incremented by two when an address is popped from the Stack with return from subroutine RET or

return from interrupt RETI.

RAM Page Z Select Register - RAMPZ

The RAMPZ register is normally used to select which 64K RAM Page is accessed by the Z pointer. As the ATmega603/103

does not support more than 64K of SRAM memory, this register is used only to select which page in the program memory

is accessed when the ELPM instruction is used. The different settings of the RAMPZ0 bit have the following effects:

Note that LPM is not affected by the RAMPZ setting.

The ATmega603 does not contain the RAMPZ register, and it does not have the ELPM instruction. The ordinary LPM

instruction can reach the entire program memory in the ATmega603.

MCU Control Register - MCUCR

The MCU Control Register contains control bits for general MCU functions.

•

Bit 7 - SRE: External SRAM Enable

When the SRE bit is set (one), the external data SRAM is enabled, and the pin functions AD0-7 (Port A), and A8-15 (Port

C) are activated as the alternate pin functions. Then the SRE bit overrides any pin direction settings in the respective data

direction registers. When the SRE bit is cleared (zero), the external data SRAM is disabled, and the normal pin and data

direction settings are used.

•

Bit 6 - SRW: External SRAM Wait State

When the SRW bit is set (one), a one cycle wait state is inserted in the external data SRAM access cycle. When the SRW

bit is cleared (zero), the external data SRAM access is executed with a three-cycle scheme. See Figure 51.External

SRAM Access Cycle without wait states73 and Figure 52.External SRAM Access Cycle with wait state74.

•

Bit 5 - SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the

MCU entering the sleep mode unless it is the programmers purpose, it is recommended to set the Sleep Enable SE bit just

before the execution of the SLEEP instruction.

Bit

7

6

5

4

3

2

1

0

$3B ($5B)

-

-

-

-

-

-

-

RAMPZ0

RAMPZ

Read/Write

R

R

R

R

R

R

R

R/W

Initial value

0

0

0

0

0

0

0

0

RAMPZ0 = 0:

Program memory address $0000- $7FFF (lower 64K bytes) is accessed by ELPM

RAMPZ0 = 1:

Program memory address $8000- $FFFF (higher 64K bytes) is accessed by ELPM

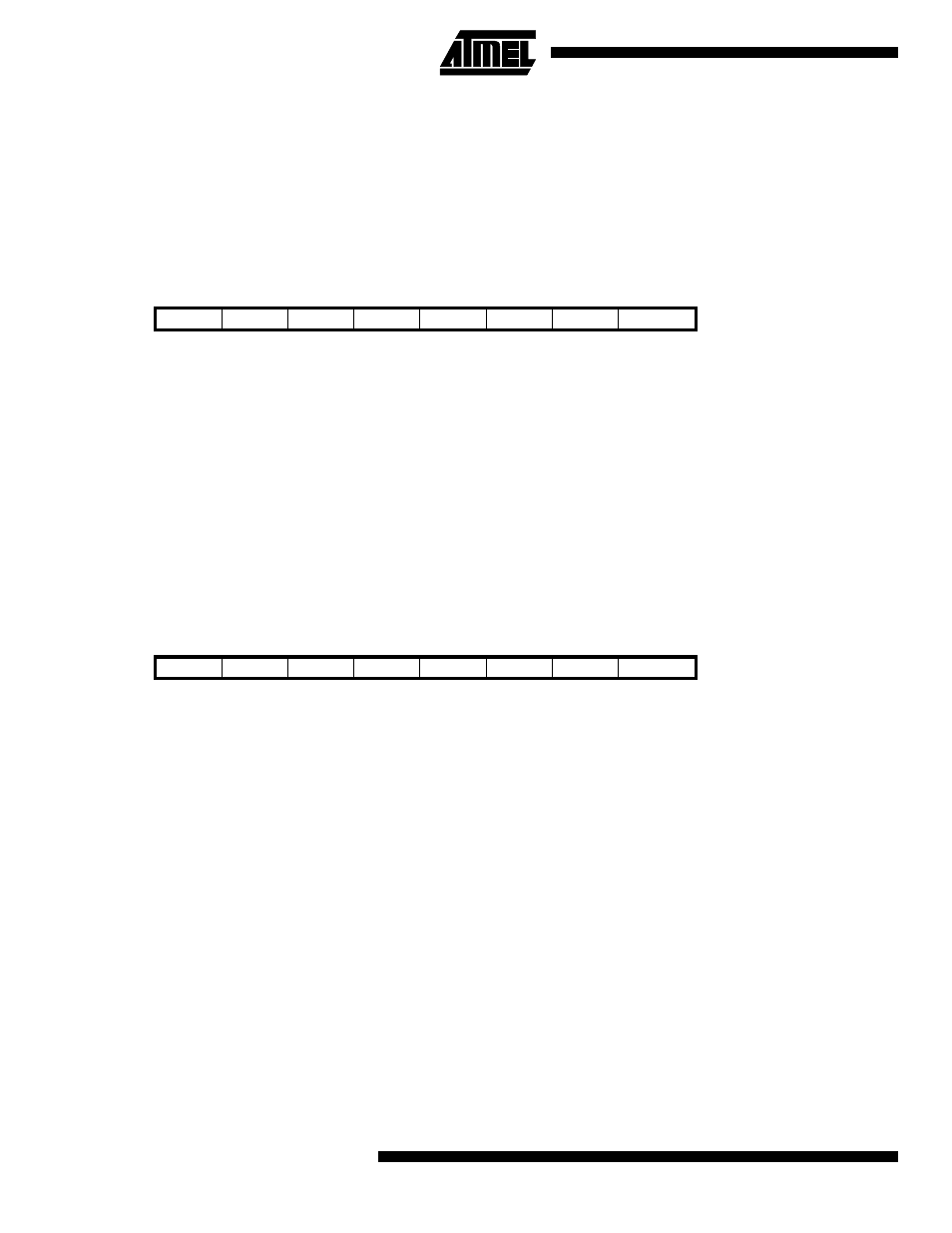

Bit

7

6

5

4

3

2

1

0

$35 ($55)

SRE

SRW

SE

SM1

SM0

-

-

-

MCUCR

Read/Write

R/W

R/W

R/W

R/W

R/W

R

R

R

Initial value

0

0

0

0

0

0

0

0