E1 information registers, 3 e1 i, Nformation – Rainbow Electronics DS21458 User Manual

Page 69: Egisters, 3 e1 information registers

DS21455/DS21458 Quad T1/E1/J1 Transceivers

69 of 270

11.3 E1 Information Registers

Register Name:

INFO3

Register Description:

Information Register 3

Register Address:

12h

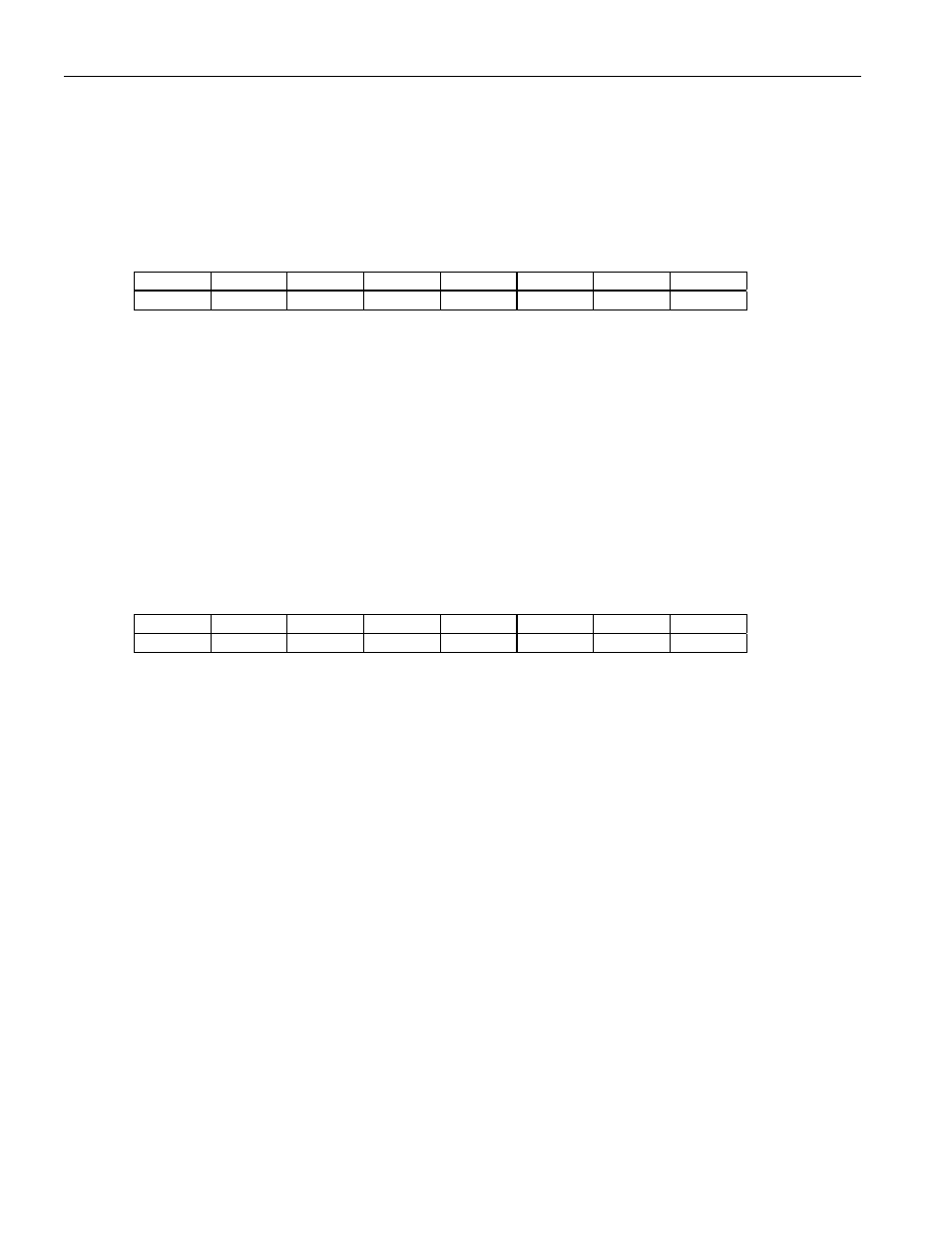

Bit

# 7 6 5 4 3 2 1 0

Name — — — — —

CRCRC

FASRC

CASRC

Default

0 0 0 0 0 0 0 0

Bit 0/CAS Resync Criteria Met Event (CASRC). Set when two consecutive CAS MF alignment words are received in error.

(Note: During a CRC resync the FAS synchronizer is brought online to verify the FAS alignment. If during this process a

FAS emulator exists, the FAS synchronizer may temporarily align to the emulator. The FASRC will go active indicating a

search for a valid FAS has been activated.)

Bit 1/FAS Resync Criteria Met Event (FASRC. Set when three consecutive FAS words are received in error.

Bit 2/CRC Resync Criteria Met Event (CRCRC). Set when 915/1000 codewords are received in error.

Register Name:

INFO7

Register Description:

Information Register 7 (Real Time)

Register Address:

30h

Bit

# 7 6 5 4 3 2 1 0

Name CSC5 CSC4 CSC3 CSC2 CSC0 FASSA

CASSA

CRC4SA

Default

0 0 0 0 0 0 0 0

Bit 0/CRC-4 MF Sync Active (CRC4SA). Set while the synchronizer is searching for the CRC-4 MF alignment word.

Bit 1/CAS MF Sync Active (CASSA). Set while the synchronizer is searching for the CAS MF alignment word.

Bit 2/FAS Sync Active (FASSA). Set while the synchronizer is searching for alignment at the FAS level.

Bit 3 to 7/CRC-4 Sync Counter Bits (CSC0 and CSC2 to CSC4). The CRC-4 sync counter increments each time the 8ms-

CRC-4 multiframe search times out. The counter is cleared when the framer has successfully obtained synchronization at the

CRC-4 level. The counter can also be cleared by disabling the CRC-4 mode (E1RCR1.3 = 0). This counter is useful for

determining the amount of time the framer has been searching for synchronization at the CRC-4 level. ITU G.706 suggests that

if synchronization at the CRC-4 level cannot be obtained within 400ms, then the search should be abandoned and proper action

taken. The CRC-4 sync counter will rollover. CSC0 is the LSB of the 6-bit counter. (Note: The second LSB, CSC1, is not

accessible. CSC1 is omitted to allow resolution to >400ms using 5 bits.)