Figure 3-2. ds21455 block diagram – Rainbow Electronics DS21458 User Manual

Page 16

DS21455/DS21458 Quad T1/E1/J1 Transceivers

16 of 270

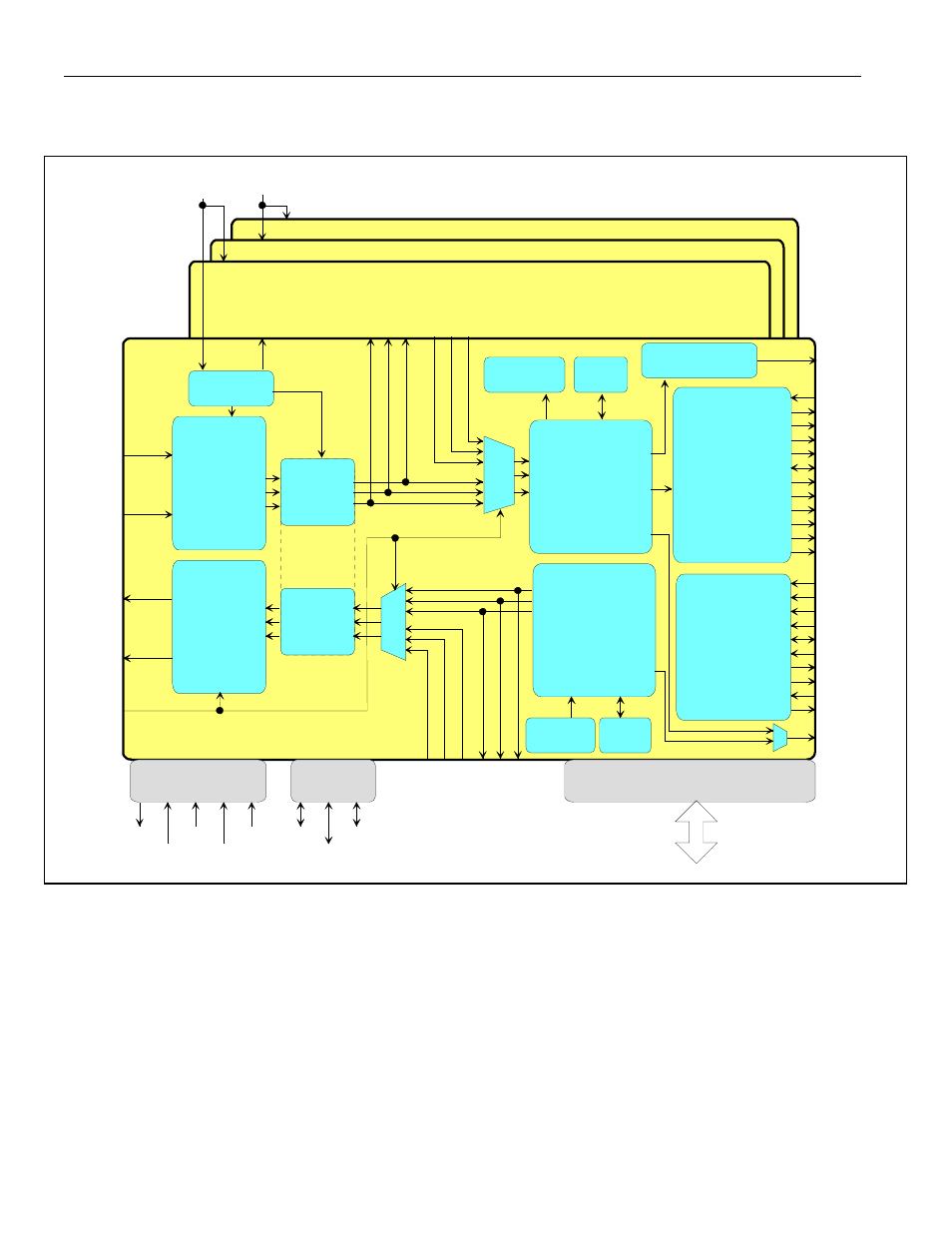

Figure 3-2. DS21455 Block Diagram

RECEIVE

FRAMER

RECEIVE

BACKPLANE

INTERFACE

TRANSMIT

BACKPLANE

INTERFACE

TRANSMIT

BACKPLANE

INTERFACE

ELASTIC STORES

SIGNALING BUFFERS

INTERLEAVE BUS

RATE CONVERSION

2 HDLCs

2 HDLCs

TRANSMIT

FRAMER

ELASTIC STORES

SIGNALING BUFFERS

INTERLEAVE BUS

RATE CONVERSION

SYNCHRONIZATION

ALARM MONITORING

SIGNALING EXTRACTION

HDLC EXTRACTION

DS0 CONDITIONING

HDB3/B8ZS DECODER

FRAMING

CRC RECALCULAION(E1)

ALARM INSERTION

SIGNALING INSERTION

HDLC INSERTION

DS0 CONDITIONING

HDB3/B8ZS CODER

JITTER

ATTEN.

RECEIVE

LIU

TRANSMIT

LIU

CLOCK & DATA

RECOVERY

WAVESHAPE

GENERATION

MASTER

CLOCK

CPU INTERFACE

MUX/NON-MUX, INTEL/MOTOROLA

JTAG

MUX

TRANSMIT

OR RECEIVE

PATH

BERT

BERT

BACKPLANE

CLOCK

MUX

RCLK

RSER

RSIG

RSIGF

RSYNC

RFSYNC

RMSYNC

RCHCLK

RCHBLK

BPCLK

RSYSCLK

TSYSCLK

TCLK

TSER

TSIG

TSYNC

TSSYNC

TCHCLK

TCHBLK

RTIP

RRING

TTIP

TRING

LIUC/TPD

TPOSI

TNEGI

TCLKI

TPOSI

TPOSI

TNEGO

TCLKO

TPOSO

RNEGI

RCLKI

RPOSI

RNEGO

RCLKO

RPOSO

8XCLK

TLCLK

TLINK

RLCLK

RLINK

ESIB

RLOS/LOTC

MCLK1 MCLK2

TRANSCEIVER #2

TRANSCEIVER #3

TRANSCEIVER #4

ESIBS0

ESIBS1

ESIBRD

JTDO

JTDI

JTCLK

JTRST

JTMS

JITTER

ATTEN.

DS21455