Rainbow Electronics DS21458 User Manual

Page 44

DS21455/DS21458 Quad T1/E1/J1 Transceivers

44 of 270

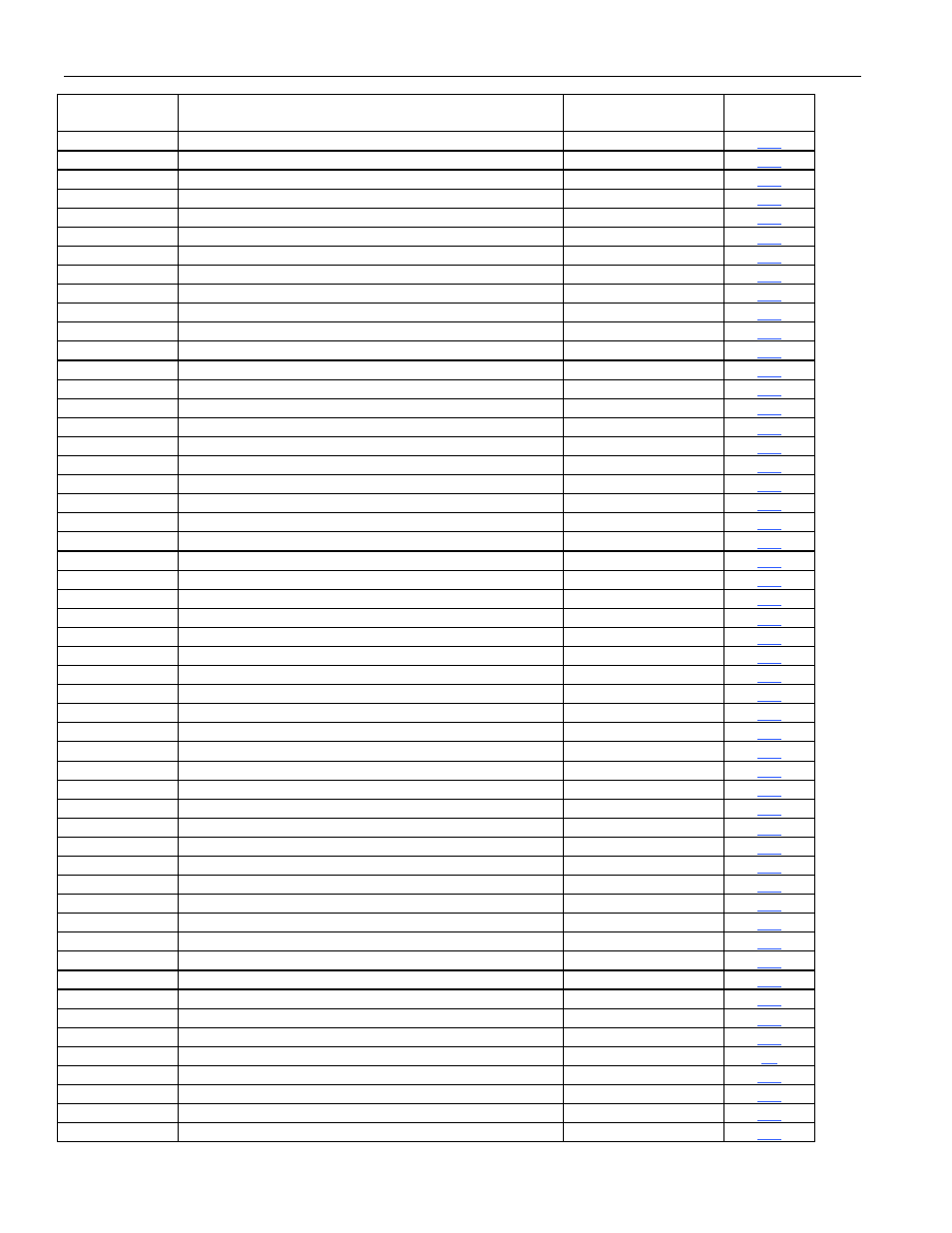

ADDRESS REGISTER

NAME

REGISTER

ABBREVIATION

PAGE

94

HDLC #1 Receive Channel Select 3

H1RCS3

95

HDLC #1 Receive Channel Select 4

H1RCS4

96

HDLC #1 Receive Time Slot Bits/Sa Bits Select

H1RTSBS

97

HDLC #1 Transmit Channel Select1

H1TCS1

98

HDLC #1 Transmit Channel Select 2

H1TCS2

99

HDLC #1 Transmit Channel Select 3

H1TCS3

9A

HDLC #1 Transmit Channel Select 4

H1TCS4

9B

HDLC #1 Transmit Time Slot Bits/Sa Bits Select

H1TTSBS

9C

HDLC #1 Receive Packet Bytes Available

H1RPBA

9D

HDLC #1 Transmit FIFO

H1TF

9E

HDLC #1 Receive FIFO

H1RF

9F

HDLC #1 Transmit FIFO Buffer Available

H1TFBA

A0

HDLC #2 Transmit Control

H2TC

A1

HDLC #2 FIFO Control

H2FC

A2

HDLC #2 Receive Channel Select 1

H2RCS1

A3

HDLC #2 Receive Channel Select 2

H2RCS2

A4

HDLC #2 Receive Channel Select 3

H2RCS3

A5

HDLC #2 Receive Channel Select 4

H2RCS4

A6

HDLC #2 Receive Time Slot Bits/Sa Bits Select

H2RTSBS

A7

HDLC #2 Transmit Channel Select 1

H2TCS1

A8

HDLC #2 Transmit Channel Select 2

H2TCS2

A9

HDLC #2 Transmit Channel Select 3

H2TCS3

AA

HDLC #2 Transmit Channel Select 4

H2TCS4

AB

HDLC #2 Transmit Time Slot Bits/Sa Bits Select

H2TTSBS

AC

HDLC #2 Receive Packet Bytes Available

H2RPBA

AD

HDLC #2 Transmit FIFO

H2TF

AE

HDLC #2 Receive FIFO

H2RF

AF

HDLC #2 Transmit FIFO Buffer Available

H2TFBA

B0

Extend System Information Bus Control Register 1

ESIBCR1

B1

Extend System Information Bus Control Register 2

ESIBCR2

B2

Extend System Information Bus Register 1

ESIB1

B3

Extend System Information Bus Register 2

ESIB2

B4

Extend System Information Bus Register 3

ESIB3

B5

Extend System Information Bus Register 4

ESIB4

B6

In-Band Code Control Register

IBCC

B7

Transmit Code Definition Register 1

TCD1

B8

Transmit Code Definition Register 2

TCD2

B9

Receive Up Code Definition Register 1

RUPCD1

BA

Receive Up Code Definition Register 2

RUPCD2

BB

Receive Down Code Definition Register 1

RDNCD1

BC

Receive Down Code Definition Register 2

RDNCD2

BD

In-Band Receive Spare Control Register

RSCC

BE

Receive Spare Code Definition Register 1

RSCD1

BF

Receive Spare Code Definition Register 2

RSCD2

C0 Receive

FDL

Register

RFDL

C1 Transmit

FDL

Register

TFDL

C2

Receive FDL Match Register 1

RFDLM1

C3

Receive FDL Match Register 2

RFDLM2

C4

Unused. Must be set = 00h for proper operation

—

—

C5

Interleave Bus Operation Control Register

IBOC

C6

Receive Align Frame Register

RAF

C7

Receive Nonalign Frame Register

RNAF

C8

Receive Si Align Frame

RSiAF