Texas Instruments TMS320TCI648x User Manual

Page 91

www.ti.com

4.3.4

Error, Reset, and Special Event Interrupt Condition Status and Clear Registers

Interrupt Conditions

Table 36. Interrupt Conditions Shown in LSU_ICSR and Cleared With LSU_ICCR (continued)

Bit

Associated LSU

Interrupt Condition

6

LSU1

Retry Doorbell response received or Atomic test-and-swap was not allowed (semaphore in

use)

5

LSU1

Transaction was not sent due to DMA data transfer error

4

LSU1

Transaction timeout occurred

3

LSU1

Transaction was not sent due to unsupported transaction type or invalid field encoding

2

LSU1

Transaction was not sent due to Xoff condition

1

LSU1

Non-posted transaction received ERROR response, or error in response payload

0

LSU1

Transaction complete, No errors (posted/non-posted)

(1)

The ICSR and the ICCR for the SRIO ports are shown in

. As described in

, each of the

nonreserved status and clear bits corresponds to a particular interrupt condition in one or more of the

SRIO ports. The ICS bits of ERR_RST_EVNT_ICSR indicate the occurrence of the conditions. The ICC

bits of ERR_RST_EVNT_ICCR are used to clear the corresponding ICS bits.

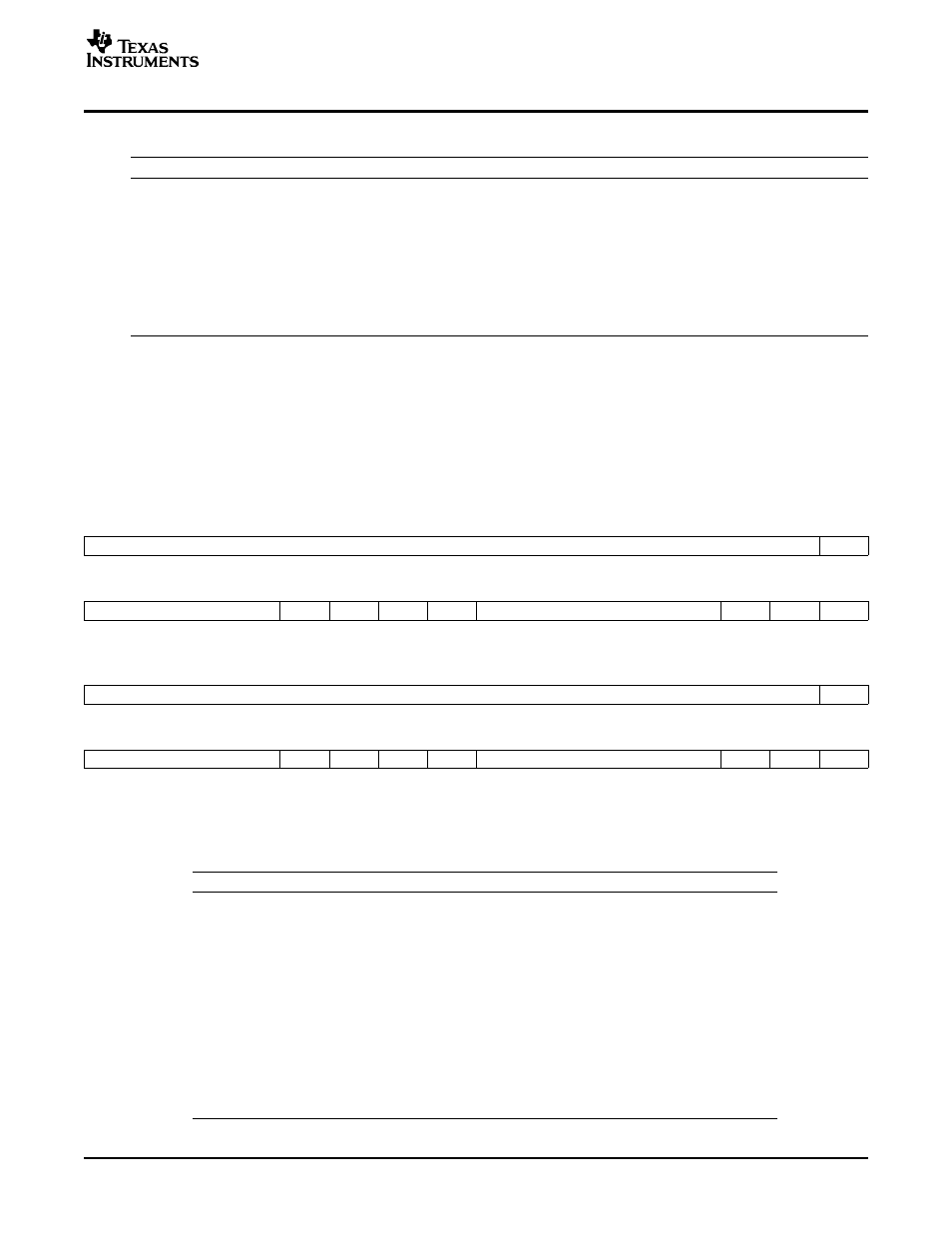

Figure 53. Error, Reset, and Special Event Interrupt Condition Status and Clear Registers

Error, Reset, and Special Event Interrupt Condition Status Register (ERR_RST_EVNT_ICSR) (Address Offset 0270h)

31

17

16

Reserved

ICS16

R-0

R-0

15

12

11

10

9

8

7

3

2

1

0

Reserved

ICS11

ICS10

ICS9

ICS8

Reserved

ICS2

ICS1

ICS0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

Error, Reset, and Special Event Interrupt Condition Clear Register (ERR_RST_EVNT_ICCR) (Address Offset 0278h)

31

17

16

Reserved

ICC16

R-0

W-0

15

12

11

10

9

8

7

3

2

1

0

Reserved

ICC11

ICC10

ICC9

ICC8

Reserved

ICC2

ICC1

ICC0

R-0

W-0

W-0

W-0

W-0

R-0

W-0

W-0

W-0

LEGEND: R = Read only; W = Write only; -n = Value after reset

Table 37. Interrupt Conditions Shown in ERR_RST_EVNT_ICSR and Cleared

With ERR_RST_EVNT_ICCR

Bit

Interrupt Condition

31–17

Reserved

16

Device reset interrupt from any port

15–12

Reserved

11

Port 3 error (TMS320TCI6482 Only)

10

Port 2 error (TMS320TCI6482 Only)

9

Port 1 error

8

Port 0 error

7–3

Reserved

2

Logical layer error management event capture

1

Port-write-in request received on any port

0

Multi-cast event control symbol interrupt received on any port

SPRUE13A – September 2006

Serial RapidIO (SRIO)

91