Diagram – Texas Instruments TMS320TCI648x User Manual

Page 27

www.ti.com

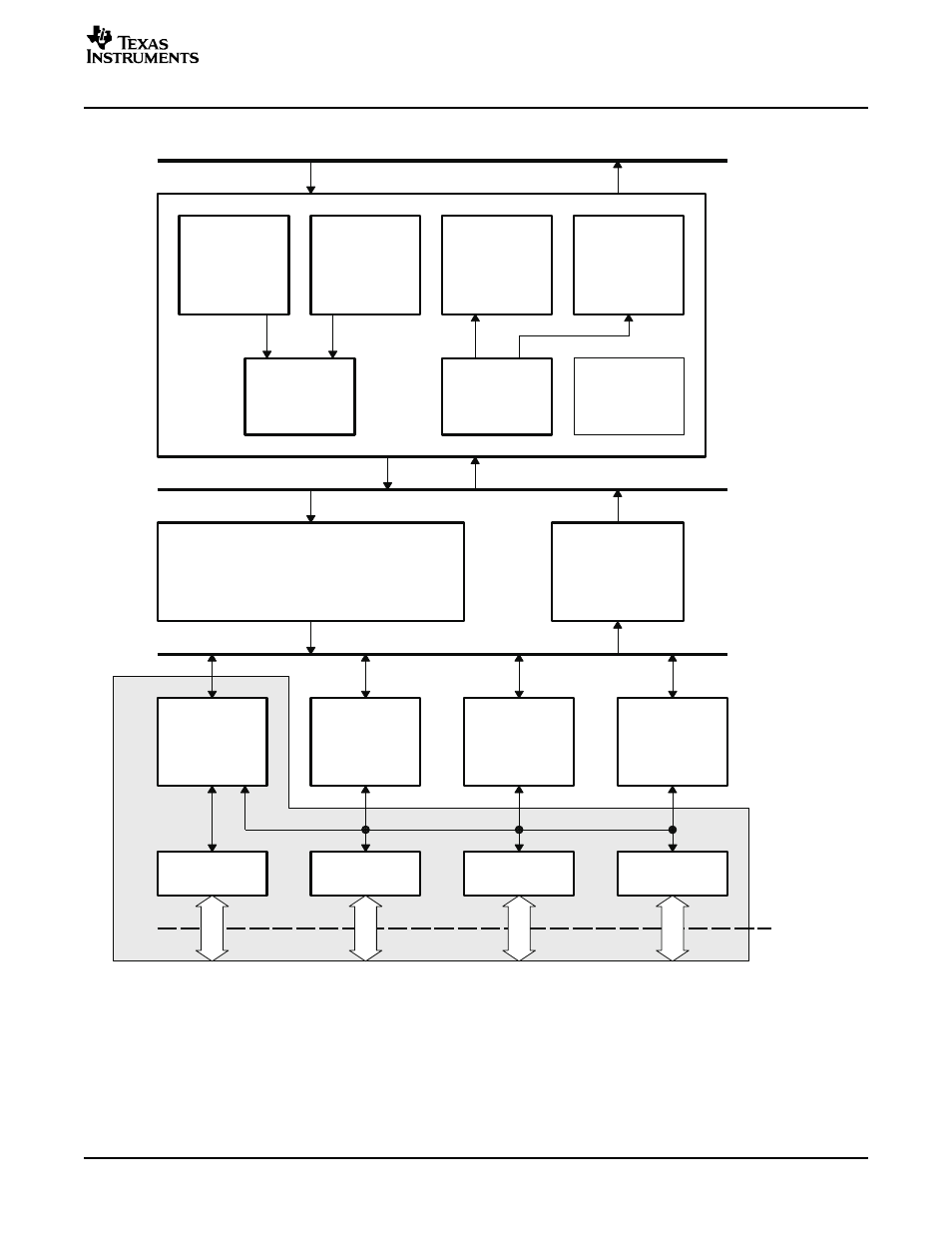

Port 0

8 x 276 TX

8 x 276 RX

8 x 276 RX

8 x 276 TX

Port 1

8 x 276 TX

8 x 276 RX

Port 2

8 x 276 RX

8 x 276 TX

Port 3

Physical

layer

buffers

SERDES 0

SERDES 1

SERDES 2

SERDES 3

SERDES

differential

signals

4x mode

data path

TX buffering

32 x 276B

8 buffers per 1X port - all priorities

32 buffers per 4X port - 8 per priority

Transaction

mapping

layer

buffers

Logical

Load/Store

units (LSUs)

TX direct I/O

Maintenance

Messaging

TXU

RX direct I/O

(MAU)

Memory

access unit

RXU

Messaging

buffer

4.5 KB TX

shared

buffer

shared

4.5 KB RX

handle

Queue

DMA bus

UDI

SRIO Functional Description

Figure 8. SRIO Component Block Diagram

SPRUE13A – September 2006

Serial RapidIO (SRIO)

27

See also other documents in the category Texas Instruments Hardware:

- Digital Signal Processor SM320F2812-HT (153 pages)

- MSP430x1xx (440 pages)

- Laser And Motor Drives DRV8811EVM (13 pages)

- TMS320 DSP (88 pages)

- MSP430x11x1 (45 pages)

- TVP5154EVM (55 pages)

- TMS320DM646X DMSOC (64 pages)

- CC2511 (24 pages)

- SN65HVS880 (4 pages)

- TPS650231EVM (14 pages)

- TSC2007EVM-PDK (16 pages)

- UCC38500EVM (16 pages)

- TMS320C6000 (62 pages)

- SCAU020 (21 pages)

- TPS40051 (17 pages)

- TNETE2201 (14 pages)

- TMS320C64x DSP (306 pages)

- UCC2891 (21 pages)

- TMS320C3x (757 pages)

- MSP430 (138 pages)

- TMS320C6712D (102 pages)

- MSP430x4xx (512 pages)

- TMS320C6454 (225 pages)

- SPRU938B (48 pages)

- TUSB3210 (22 pages)

- TMS320C6457 (43 pages)

- CC2530ZNP (3 pages)

- TMS320C6455 (50 pages)

- TSB12LV26 (91 pages)

- TMS320C6472 (2 pages)

- VLYNQ Port (49 pages)

- TMS380C26 (92 pages)

- MSP-FET430 (95 pages)

- TMS320TCI6486 (160 pages)

- TPS2330 (22 pages)

- DM648 DSP (47 pages)

- TMS320DM36X (134 pages)

- MSC1211 (35 pages)

- SPRAA56 (29 pages)

- DAC7741EVM (28 pages)

- CDCM7005 (34 pages)

- TMS370 (99 pages)

- Adpater (37 pages)

- TMS320C6452 DSP (46 pages)