12 tx buffers, credit, and packet reordering, 1 multiple ports with 1x operation – Texas Instruments TMS320TCI648x User Manual

Page 75

www.ti.com

2.3.12

TX Buffers, Credit, and Packet Reordering

2.3.12.1

Multiple Ports With 1x Operation

SRIO Functional Description

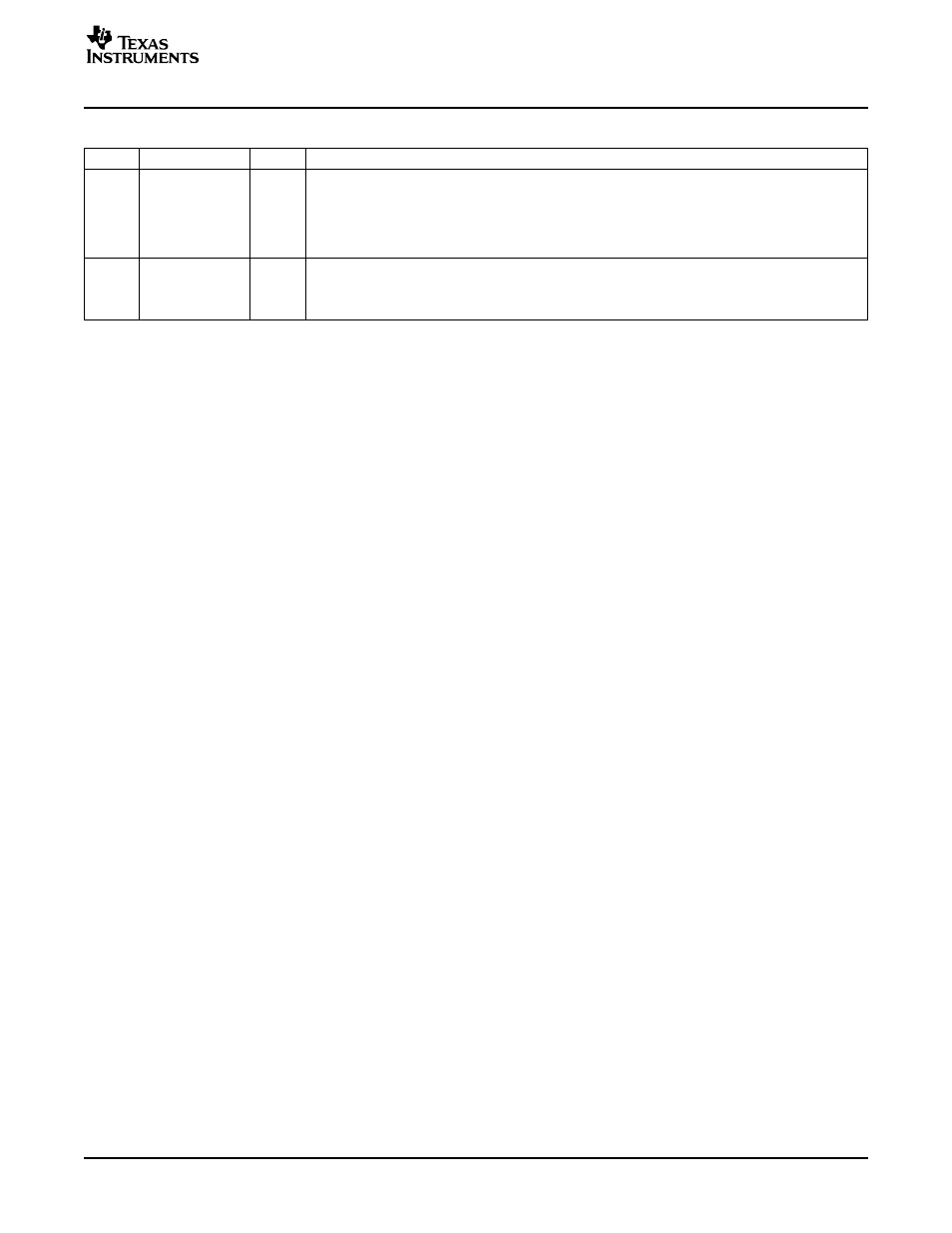

Table 29. Peripheral Control Register (PCR) Field Descriptions (continued)

Bit

Field

Value

Description

1

SOFT

Soft stop. This bit and the FREE bit determine how the SRIO peripheral behaves during emulation

halts.

0

Hard stop. All status registers are frozen in default state. (This mode is not supported on the SRIO

peripheral.)

1

Soft stop

0

FREE

Free run

0

The SOFT bit takes effect.

1

Free run. Peripheral ignores the emulation suspend signal and functions normally.

Free Run Mode: (default mode) Peripheral does not respond to an emulation suspend assertion. The

peripheral functions normally, irrespective of the CPU emulation state.

Soft Stop Mode: The peripheral gracefully halts operations. The peripheral halts operation at a point that

makes sense both to the internal DMA/data access operation and to the pin interface as described below,

after finishing packet reception or transmission in progress:

•

DMA bus DMA master: DMA bus requests in progress are allowed to complete (DMA bus has no

means to throttle command in progress from the master). DMA bus requests that correspond to the

same network packet are allowed to complete. No new DMA bus requests will be generated on the

next new packet.

•

Configuration bus MMR interface: All memory-mapped register (MMR) configuration bus requests

are serviced as normal.

•

Events/interrupts: New events/interrupts are not generated to the CPU for newly arriving packets.

Current transactions are allowed to finish and may cause an interrupt upon completion.

•

Slave pin interface: The pin interface functions as normal. If buffering is available in the peripheral,

the peripheral services externally generated requests as long as possible. When the internal buffers

are consumed, the peripheral will retry incoming network packets in the physical layer.

•

Master pin interface: No new master requests are generated. Master requests in progress are

allowed to complete, including all packets located in the physical layer transmit buffers.

Hard Stop Mode: The peripheral halts immediately. This mode is not supported in the peripheral.

Packets to be transmitted by the SRIO peripheral travel to logical layer buffers. The packets are then

moved from the logical layer buffers to physical layer buffers. From the physical layer buffers, the packets

are transmitted through a port to a connected device.

With multiple ports in 1x mode, logical layer buffers are grouped per port and contain all priorities. Each

group is 8 buffers deep. A counter is maintained for each port to track available buffer credit across the

UDI. The count is initialized to 8 credits per port. The count is decremented each time a packet is sent

across the UDI for a port. Each port buffer group has a buffer release signal which indicates the release of

a packet from the logical layer buffer to the port's physical buffer, thus indicating the freeing up of space in

the port's logical buffer.

Thresholds are used to govern outbound credit when requested by the protocol units (MAU, RXU, TXU,

and the LSUs). These thresholds are programmable in the peripheral settings control register

(PER_SET_CNTL at address offset 0020h).

The physical layer buffer tries to process all packets in the order they were sent across the UDI. However,

it is also governed by a re-ordering algorithm to decide which packets may be sent to the physical layer

buffer depending on credit availability there.

SPRUE13A – September 2006

Serial RapidIO (SRIO)

75