1 detailed description, 093ch) – Texas Instruments TMS320TCI648x User Manual

Page 66

www.ti.com

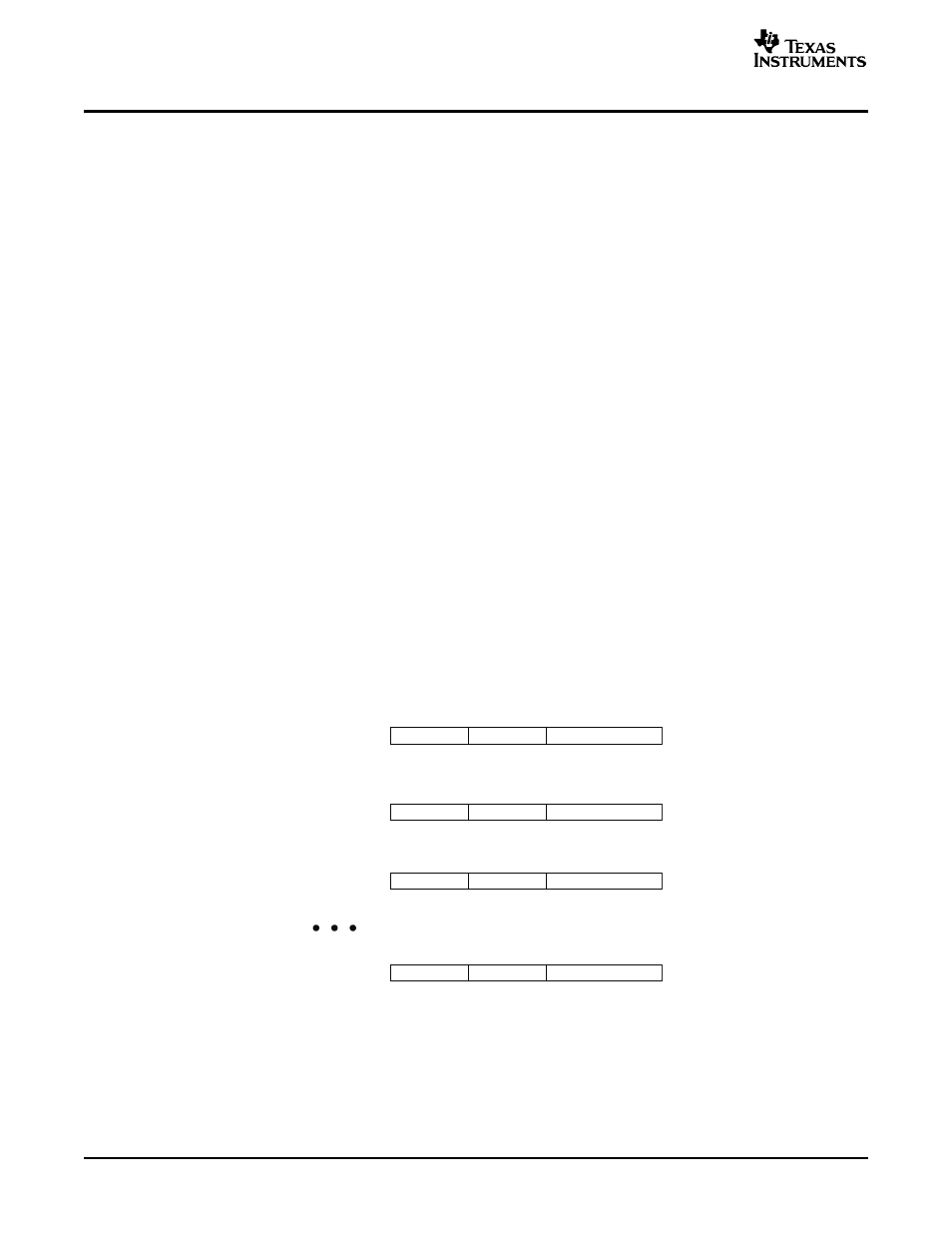

2.3.8.1

Detailed Description

Reserved

FLOW_CNTL0

31-18

R-0x00000

TT

17-16

R/W-01

FLOW_CNTL_ID

15-0

R/W-0x0000

Reserved

FLOW_CNTL1

31-18

R-0x00000

TT

17-16

R/W-01

FLOW_CNTL_ID

15-0

R/W-0x0000

Reserved

FLOW_CNTL2

31-18

R-0x00000

TT

17-16

R/W-01

FLOW_CNTL_ID

15-0

R/W-0x0000

Reserved

FLOW_CNTL15

31-18

R-0x00000

TT

17-16

R/W-01

FLOW_CNTL_ID

15-0

R/W-0x0000

SRIO Functional Description

Since CCPs do not have guaranteed delivery and can be dropped by the fabric, an implicit method of

enabling an Xoff’d flow must exist. A simple timeout method is used. Additionally, flow control checks can

be enabled or disabled through the Transmit Source Flow Control Masks. Received CCPs are not passed

through the DMA bus interface.

To avoid large and complex table management, a basic scheme is implemented for congestion

management. The primary goal is to avoid large parallel searches of a centralized congested route table

for each outgoing packet request. The congested route table requirements and subsequent searches

would be overwhelming if each possible DESTID and PRIORITY combination had its own entry. To

implement a more basic scheme, the following assumptions have been made:

•

A small number of flows constitute the majority of traffic, and these flows are most likely to cause

congestion

•

HOL blocking is undesired, but allowable for TX CPPI queues

•

Flow control will be based on DESTID only, regardless of PRIORITY

The congested route table is therefore more static in nature. Instead of dynamically updating a table with

each CCP’s flow information as it arrives, a small finite-entry table is set up and configured by software to

reflect the more critical flows it is using. Only these flows have a discrete table entry. A 16 entry table

reflects 15 critical flows, leaving the sixteenth entry for general other flows, which are categorized

together.

and

summarize the DESTID table entries that are programmable by the CPU

through dedicated flow control registers. A 3-bit hardware counter is implemented for table entries 0

through 14, to maintain a count of Xoff CCPs for that flow. The other flows table entry counts Xoff CCPs

for all flows other than the discrete entries. The counter for this table entry has 5 bits. All outgoing flows

with non-zero Xoff counts are disabled. The counter value is decremented for each corresponding Xon

CCP that is received, but it is not decrement below zero. Additionally, a hardware timer exists for each

table entry to turn on flows that may have been abandoned by lost Xon CCPs. The timer value is of an

order of magnitude larger than the 32-bit Port Response Time-out CSR value. For this reason, each

transmission source adds 2 bits to its 4-bit response time-out counter. Descriptions of this type of time-out

counter are in

and

. The additional 2 bits count three timecode revolutions

and provide an implicit Xon timer equal to 3x the Response time-out counter value.

Figure 27. Flow Control Table Entry Registers (Address Offset 0900h–093Ch)

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Serial RapidIO (SRIO)

66

SPRUE13A – September 2006