Decode), Destinations, Section 5.31 – Texas Instruments TMS320TCI648x User Manual

Page 150

www.ti.com

5.31 Interrupt Status Decode Register (INTDSTn_DECODE)

SRIO Registers

There are eight of these registers, one for each interrupt destination (see

). This type of register is

shown in

and described in

. Interrupt sources are mapped to an interrupt decode

register only if the ICRRs routes the interrupt source to the corresponding physical interrupt. Each status

decode bit is a logical OR of multiple interrupt sources that are mapped to the same bit. For additional

programming see

Table 83. INTDSTn_DECODE Registers and the Associated Interrupt

Destinations

Register

Address Offset

Associated Interrupt

Destination

INTDST0_DECODE

0300h

INTDST0

INTDST1_DECODE

0304h

INTDST1

INTDST2_DECODE

0308h

INTDST2

INTDST3_DECODE

030Ch

INTDST3

INTDST4_DECODE

0310h

INTDST4

INTDST5_DECODE

0314h

INTDST5

INTDST6_DECODE

0318h

INTDST6

INTDST7_DECODE

031Ch

INTDST7

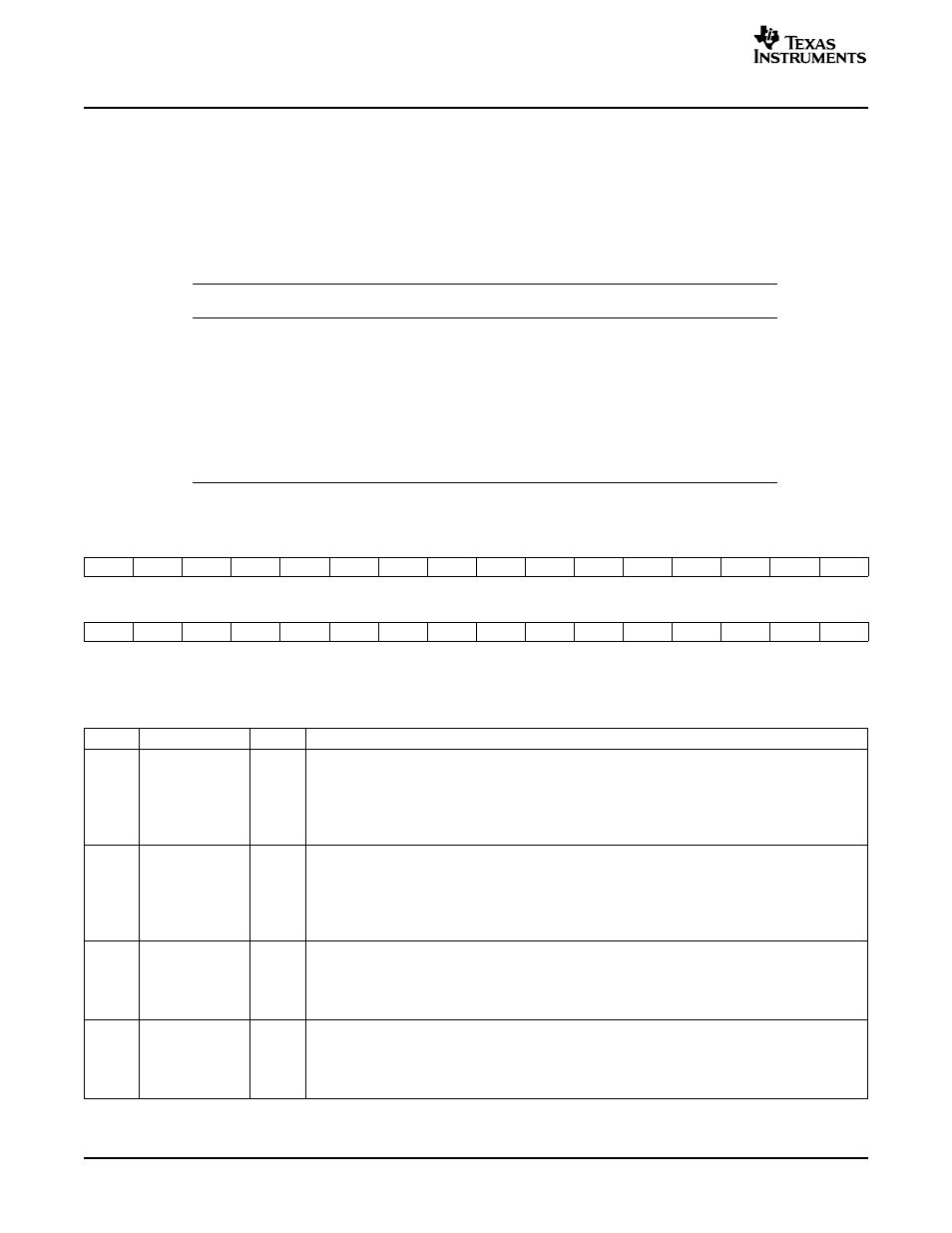

Figure 92. Interrupt Status Decode Register (INTDSTn_DECODE)

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

ISD31

ISD30

ISD29

ISD28

ISD27

ISD26

ISD25

ISD24

ISD23

ISD22

ISD21

ISD20

ISD19

ISD18

ISD17

ISD16

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ISD15

ISD14

ISD13

ISD12

ISD11

ISD10

ISD9

ISD8

ISD7

ISD6

ISD5

ISD4

ISD3

ISD2

ISD1

ISD0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

R-0

LEGEND: R = Read, W = Write, -n = Value after reset

Table 84. Interrupt Status Decode Register (INTDSTn_DECODE) Field Descriptions

Bit

Field

Value

Description

31

ISD31

0

No interrupt request routed to this bit.

1

Interrupt request detected. Possible interrupt sources:

•

An LSU (check LSU_ICSR)

•

TX buffer descriptor queue 0 (bit 0 of TX_CPPI_ICSR)

•

RX buffer descriptor queue 0 (bit 0 of RX_CPPI_ICSR)

30

ISD30

0

No interrupt request routed to this bit.

1

Interrupt request detected. Possible interrupt sources:

•

A port (check ERR_RST_EVNT_ICSR)

•

TX buffer descriptor queue 1 (bit 1 of TX_CPPI_ICSR)

•

RX buffer descriptor queue 1 (bit 1 of RX_CPPI_ICSR)

29

ISD29

0

No interrupt request routed to this bit.

1

Interrupt request detected. Possible interrupt sources:

•

TX buffer descriptor queue 2 (bit 2 of TX_CPPI_ICSR)

•

RX buffer descriptor queue 2 (bit 2 of RX_CPPI_ICSR)

28

ISD28

0

No interrupt request routed to this bit.

1

Interrupt request detected. Possible interrupt sources:

•

TX buffer descriptor queue 3 (bit 3 of TX_CPPI_ICSR)

•

RX buffer descriptor queue 3 (bit 3 of RX_CPPI_ICSR)

150

Serial RapidIO (SRIO)

SPRUE13A – September 2006