73 port control csr n (spn_ctl), Section 5.73 – Texas Instruments TMS320TCI648x User Manual

Page 206

www.ti.com

5.73 Port Control CSR n (SPn_CTL)

SRIO Registers

Each of the four ports is supported by a register of this type (see

). The port control CSR n

(SPn_CTL) is shown in

and described in

. To change from 1 lane to 4 lanes there

are 2 registers that need to be programmed. The SP_IP_MODE (offset 0x12004) bits 31-30 are set to be

1x/4p or 4 ports (1x mode each). The PER_SET_CNTL (offset 0x0020) bit 8 is set up for port (1x/4p) or

priority based (1x mode each).

Table 148. SPn_CTL Registers and the Associated Ports

Register

Address Offset

Associated Port

SP0_CTL

115Ch

Port 0

SP1_CTL

117Ch

Port 1

SP2_CTL

119Ch

Port 2

SP3_CTL

11BCh

Port 3

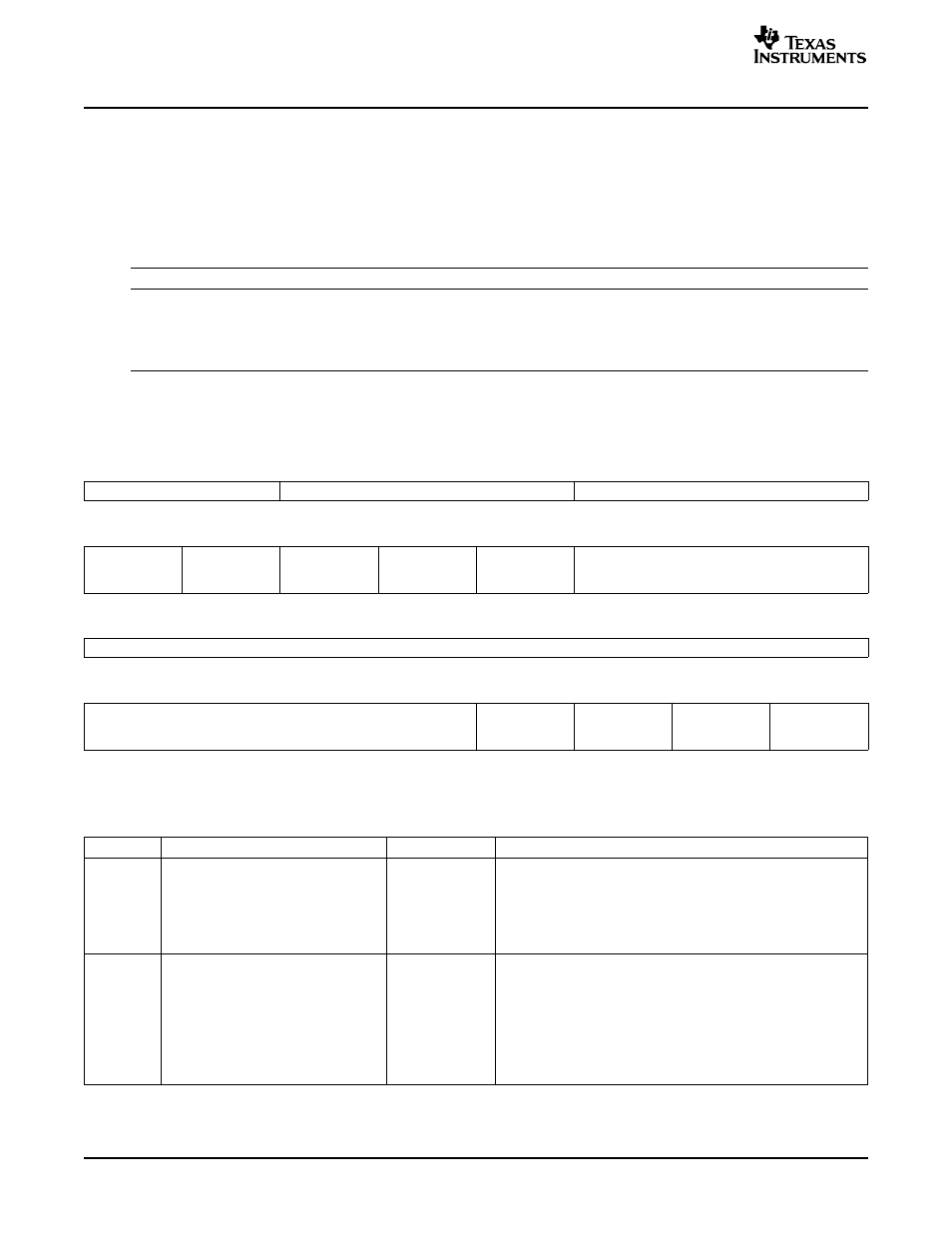

Figure 136. Port Control CSR n (SPn_CTL)

31

30 29

27 26

24

PORT_WIDTH

INITIALIZED_PORT_WIDTH

PORT_WIDTH_OVERRIDE

R-01

R-000

R/W-000

23

22

21

20

19

18

16

OUTPUT_

INPUT_

ERROR_

PORT_

MULTICAST_

PORT_

PORT_

CHECK_

Reserved

DISABLE

PARTICIPANT

ENABLE

ENABLE

DISABLE

R/W-0

R/W-0

R/W-0

R/W-0

R-0

R-0

15

8

Reserved

R-0

7

4

3

2

1

0

STOP_PORT_

DROP_

PORT_

Reserved

FLD_ENC_

PACKET_

PORT_TYPE

LOCKOUT

ENABLE

ENABLE

R-0

R/W-0

R/W-0

R/W-0

R-1

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Table 149. Port Control CSR n (SPn_CTL) Field Descriptions

Bit

Field

Value

Description

31–30

PORT_WIDTH

Port width. This read-only field indicates the hardware width of

the port.

00b

Single-lane port (valid for all ports)

01b

Four-lane port (valid for port 0 only)

1xb

Reserved

29–27

INITIALIZED_PORT_WIDTH

Initialized port width. This read-only field indicates the width of

the ports after initialization.

000b

Single-lane port, lane 0

001b

Single-lane port, lane 2 (See RapidIO Serial Spec 1.2, Chapter

4.4.10)

010b

Four-lane port

011b–111b

Reserved

206

Serial RapidIO (SRIO)

SPRUE13A – September 2006