Texas Instruments TMS320TCI648x User Manual

Page 58

www.ti.com

SRIO Functional Description

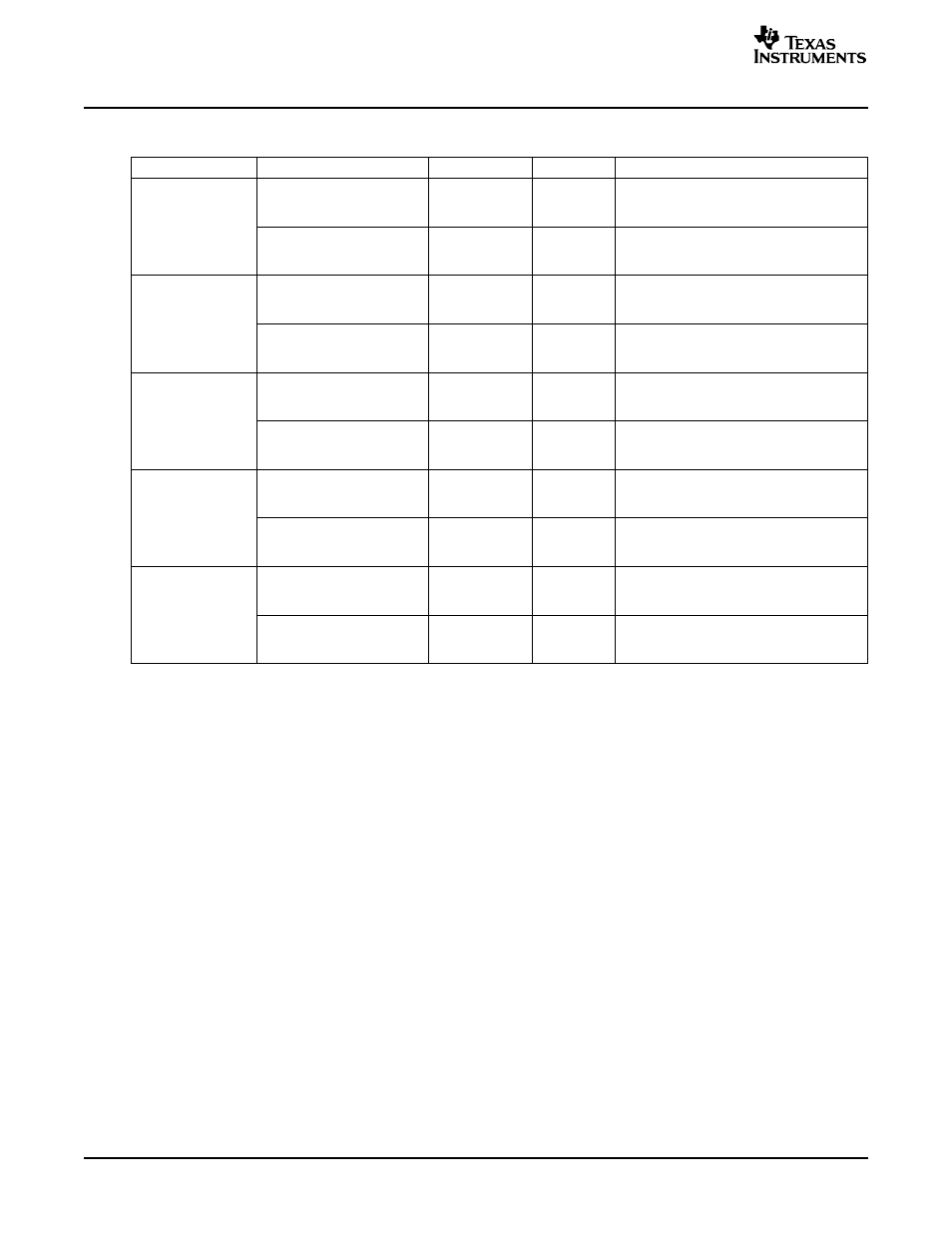

Table 22. Weighted Round Robin Programming Registers (Address Offset 7E0h–7ECh) (continued)

Field Pair

Register[Bits]

Field

Value

Description

TX_Queue_Map11

TX_QUEUE_CNTL2[27–24]

Queue Pointer

0h to Fh

Pointer to a queue. This pointer can be

programmed to point to any one of the 16

TX buffer descriptor queues.

TX_QUEUE_CNTL2[31–28]

Number of Msgs

0h to Fh

Number of contiguous messages

(descriptors) to process before moving to

TX_Queue_Map12.

TX_Queue_Map12

TX_QUEUE_CNTL3[3–0]

Queue Pointer

0h to Fh

Pointer to a queue. This pointer can be

programmed to point to any one of the 16

TX buffer descriptor queues.

TX_QUEUE_CNTL3[7–4]

Number of Msgs

0h to Fh

Number of contiguous messages

(descriptors) to process before moving to

TX_Queue_Map13.

TX_Queue_Map13

TX_QUEUE_CNTL3[11–8]

Queue Pointer

0h to Fh

Pointer to a queue. This pointer can be

programmed to point to any one of the 16

TX buffer descriptor queues.

TX_QUEUE_CNTL3[15–12]

Number of Msgs

0h to Fh

Number of contiguous messages

(descriptors) to process before moving to

TX_Queue_Map14.

TX_Queue_Map14

TX_QUEUE_CNTL3[19–16]

Queue Pointer

0h to Fh

Pointer to a queue. This pointer can be

programmed to point to any one of the 16

TX buffer descriptor queues.

TX_QUEUE_CNTL3[23–20]

Number of Msgs

0h to Fh

Number of contiguous messages

(descriptors) to process before moving to

TX_Queue_Map15.

TX_Queue_Map15

TX_QUEUE_CNTL3[27–24]

Queue Pointer

0h to Fh

Pointer to a queue. This pointer can be

programmed to point to any one of the 16

TX buffer descriptor queues.

TX_QUEUE_CNTL3[31–28]

Number of Msgs

0h to Fh

Number of contiguous messages

(descriptors) to process before moving to

TX_Queue_Map0.

The TX queues are treated differently than the RX queues. A TX queue can mix single and multi-segment

message buffer descriptors. The software manages the queue usage.

All outgoing message segments have responses that indicate the status of the transaction. Responses

may indicate DONE, ERROR or RETRY. A buffer descriptor may be released back to CPU control

(OWNERSHIP = 0), only after all segment responses are received, or alternatively if a response timeout

occurs. Timeouts and response evaluation have high priority in the state-machine since they are the only

means to release TX packet resources. The CC is set in the buffer descriptor to indicate the response

status to the CPU. If there is a RETRY response, the TX CPPI module will immediately retry the packet

before continuing to the next queue in the round-robin loop, as long as the RETRY_COUNT is not

exceeded. Once this limit is exceeded, the buffer can be released back to CPU control with the

appropriate CC set. Retry of a message segment does not imply retrying a whole message. Only

segments for which a RETRY response is received should be re-transmitted. This will involve calculating

the correct starting point within the TX data buffer based on the failed segment number and message

length. To achieve respectable performance, the peripheral must not wait for a message/segment

response before sending out the next packet.

Since RapidIO allows for out-of-order responses, the TX CPPI hardware must support this functionality. As

responses are received, the hardware updates the corresponding TX buffer descriptor to reflect the status.

However, if the response is out-of-order, the hardware does not update the CP or set the corresponding

interrupt. Only after all preceding outstanding message responses are received, will the CP and interrupt

be updated. This ensures that a contiguous block of buffer descriptors, starting at the oldest outstanding

descriptor, has been processed by the hardware and is ready for the CPU to reclaim the buffers.

58

Serial RapidIO (SRIO)

SPRUE13A – September 2006