Ctl_indep), Descriptions, Section 5.96 – Texas Instruments TMS320TCI648x User Manual

Page 236

www.ti.com

5.96 Port Control Independent Register n (SPn_CTL_INDEP)

SRIO Registers

Each of the four ports is supported by a register of this type (see

). The port control independent

register n (SPn_CTL_INDEP) is shown in

and described in

Table 182. SPn_CTL_INDEP Registers and the Associated Ports

Register

Address Offset

Associated Port

SP0_CTL_INDEP

14004h

Port 0

SP1_CTL_INDEP

14104h

Port 1

SP2_CTL_INDEP

14204h

Port 2

SP3_CTL_INDEP

14304h

Port 3

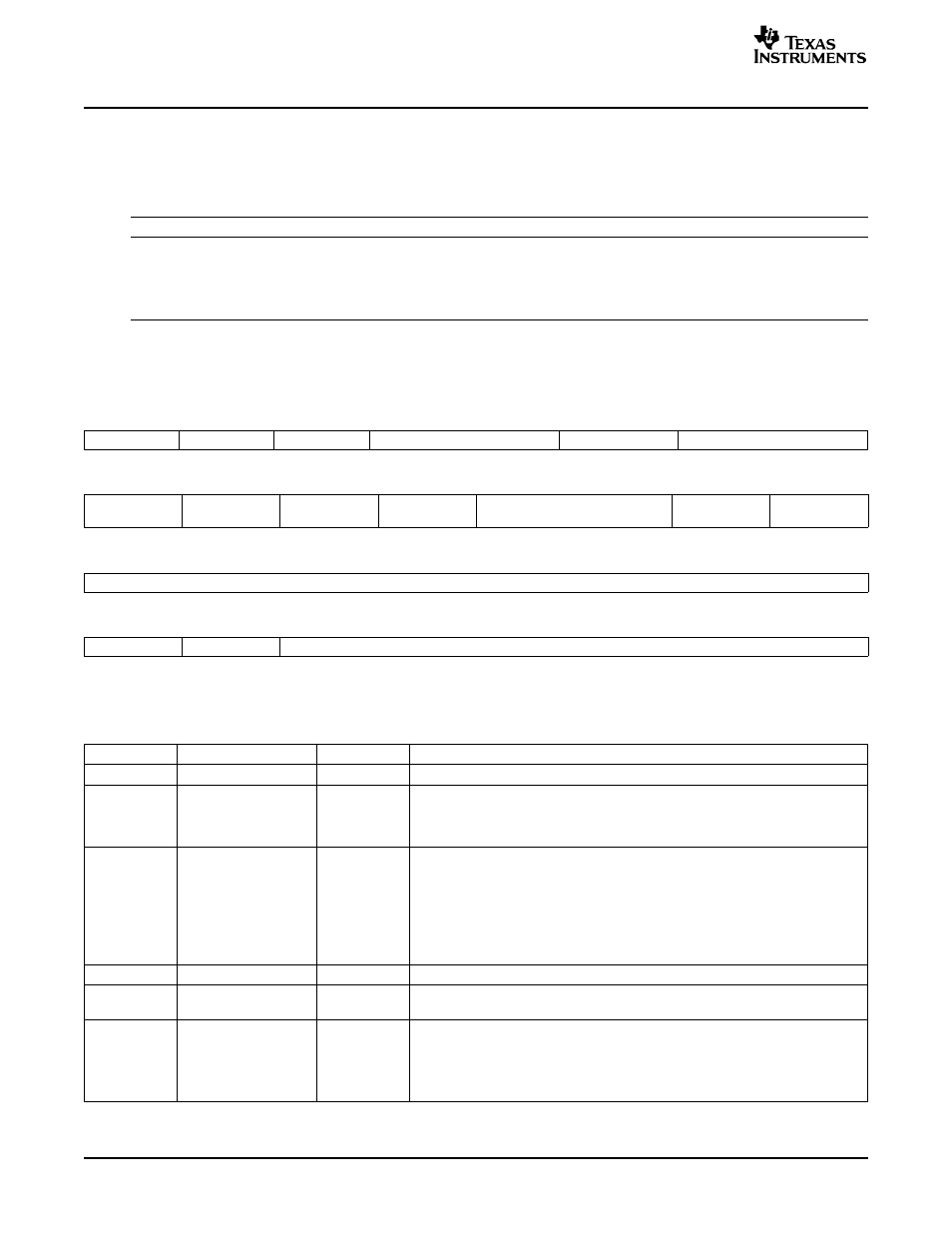

Figure 159. Port Control Independent Register n (SPn_CTL_INDEP)

31

30

29

28

27

26

25

24

Reserved

TX_FLW

SOFT_REC

Reserved

FORCE_REINIT

TRANS_MODE

R-0

R/W-0

R/W-0

R-0

W-0

R/W-01

23

22

21

20

19

18

17

16

SEND_DBG_

ILL_TRANS_

ILL_TRANS_

MAX_RETRY_

MAX_RETRY_

DEBUG

Reserved

PKT

EN

ERR

EN

ERR

R/W-0

R/W-0

R/W-0

R/W-0

R-0

R/W-0

R/W-0

15

8

MAX_RETRY_THR

R/W-00h

7

6

5

0

IRQ_EN

IRQ_ERR

Reserved

R/W-0

R/W-0

R-0

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Table 183. Port Control Independent Register n (SPn_CTL_INDEP) Field Descriptions

Bit

Field

Value

Description

31

Reserved

0

This read-only bit returns 0 when read.

30

TX_FLW

Transmit Link Flow Control enable

0

Disables transmit flow control (Enables receive link flow control)

1

Reserved

29

SOFT_REC

Software controlled error recovery

0

Transmission of error recovery sequence is performed by the hardware

1

Transmission of error recovery sequence is performed by the software. By

default the transmission error recovery sequence is performed by the hardware.

If this bit is set, the hardware recovery is disabled and the hardware

transmission logic must wait until software has written the register Port n Local

ackID Status CSR.

28–27

Reserved

0

These read-only bits return 0s when read.

26

FORCE_REINIT

Force reinitialization process. In 4x mode this bit affects all 4 lanes. This bit is

write only, and reads always return 0.

25–24

TRANS_MODE

Describes the transfer mode for each port.

00b

Reserved (Cut-Through Mode)

01b

Store & Forward Mode

1xb

Reserved

236

Serial RapidIO (SRIO)

SPRUE13A – September 2006