36 lsun control register 3 (lsun_reg3), Reg3), Descriptions – Texas Instruments TMS320TCI648x User Manual

Page 158: Section 5.36

www.ti.com

5.36 LSUn Control Register 3 (LSUn_REG3)

SRIO Registers

There are four of these registers, one for each LSU (see

). LSUn_REG3 is shown in

and described in

. For additional programming see

Table 93. LSUn_REG3 Registers and the Associated LSUs

Register

Address Offset

Associated LSU

LSU1_REG3

040Ch

LSU1

LSU2_REG3

042Ch

LSU2

LSU3_REG3

044Ch

LSU3

LSU4_REG3

046Ch

LSU4

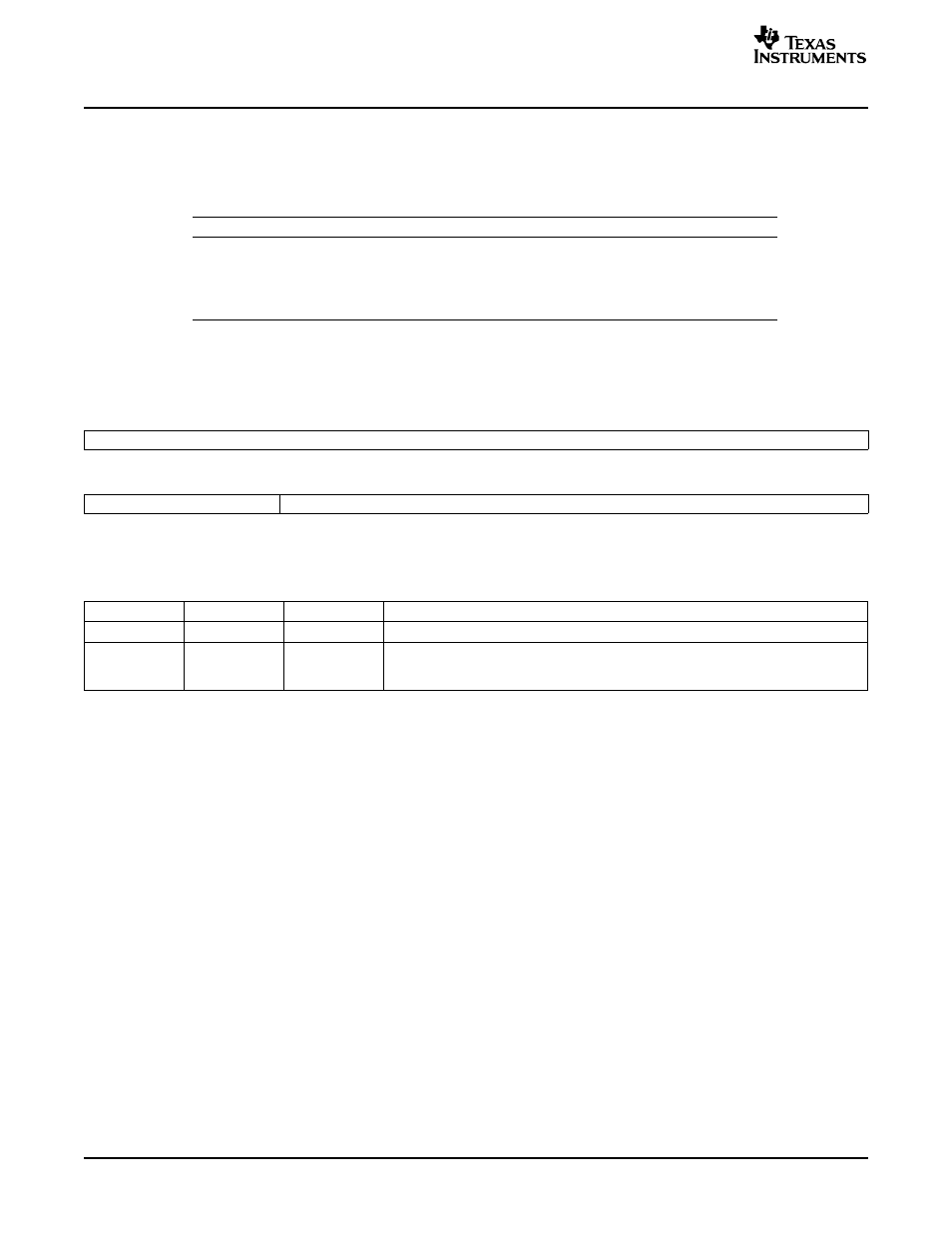

Figure 97. LSUn Control Register 3 (LSUn_REG3)

31

16

Reserved

R-0000h

15

12 11

0

Reserved

BYTE_COUNT

R-0h

R/W-000h

LEGEND: R/W = Read/Write; R = Read only; -n = Value after reset

Table 94. LSUn Control Register 3 (LSUn_REG3) Field Descriptions

Bit

Field

Value

Description

31–12

Reserved

00000h

These read-only bits return 0s when read.

11–0

BYTE_COUNT

000h–FFFh

Number of data bytes to read or write, up to 4K bytes. This value is used in

conjunction with the specified RapidIO address to create the data size and word

pointer fields in the RapidIO packet header.

Serial RapidIO (SRIO)

158

SPRUE13A – September 2006