1 rx operation – Texas Instruments TMS320TCI648x User Manual

Page 44

www.ti.com

2.3.4.1

RX Operation

Mailbox 1...64

from RapidIO packet

Header - Received on any

input port

Mailbox mapper

Q15

Q2

Q1

Q0

Queue assignable to any core

Packetsequence

Message

n

A

Packet

manager

n+1

B

n+2

B

n+3

C

n+4

D

n+5

B

n+6

E

Buffer descriptor

queues:

Descriptor per message

All priorities

Dedicated single-segment

message descriptor queue

A

C

E

D

null

null

B

Multi-segment message

descriptor queue

Multi-segment message

descriptor queue N

L2 memory

data buffer, up to 256B

n data packet

n+3 data packet

n+4 data packet

n+6 data packet

256B free buffer

L2 memory

data buffer, up to 4K

n+5 data packet

n+2 data packet

n+1 data packet

4KB free buffer

SRIO Functional Description

•

Out-of-order responses are allowed.

•

A RETRY response is issued to the first received segment of a multi-segment message when the RX

queue is busy servicing another request.

–

Subsequent RETRY responses may have to be sent for received pipeline segments or additional

pipelined messages to the same queue.

•

In-order message reception for dedicated flows is mode programmable.

•

A queue is needed for each supported simultaneous multi-segment RX message.

•

A minimum of 1.25K bytes of SRAM (64 buffer descriptors) is supported.

•

The transmit source must be able to retry any given segment of a message.

•

DestID is equal to port for TX operations, and the same DestID is not accessible from multiple ports.

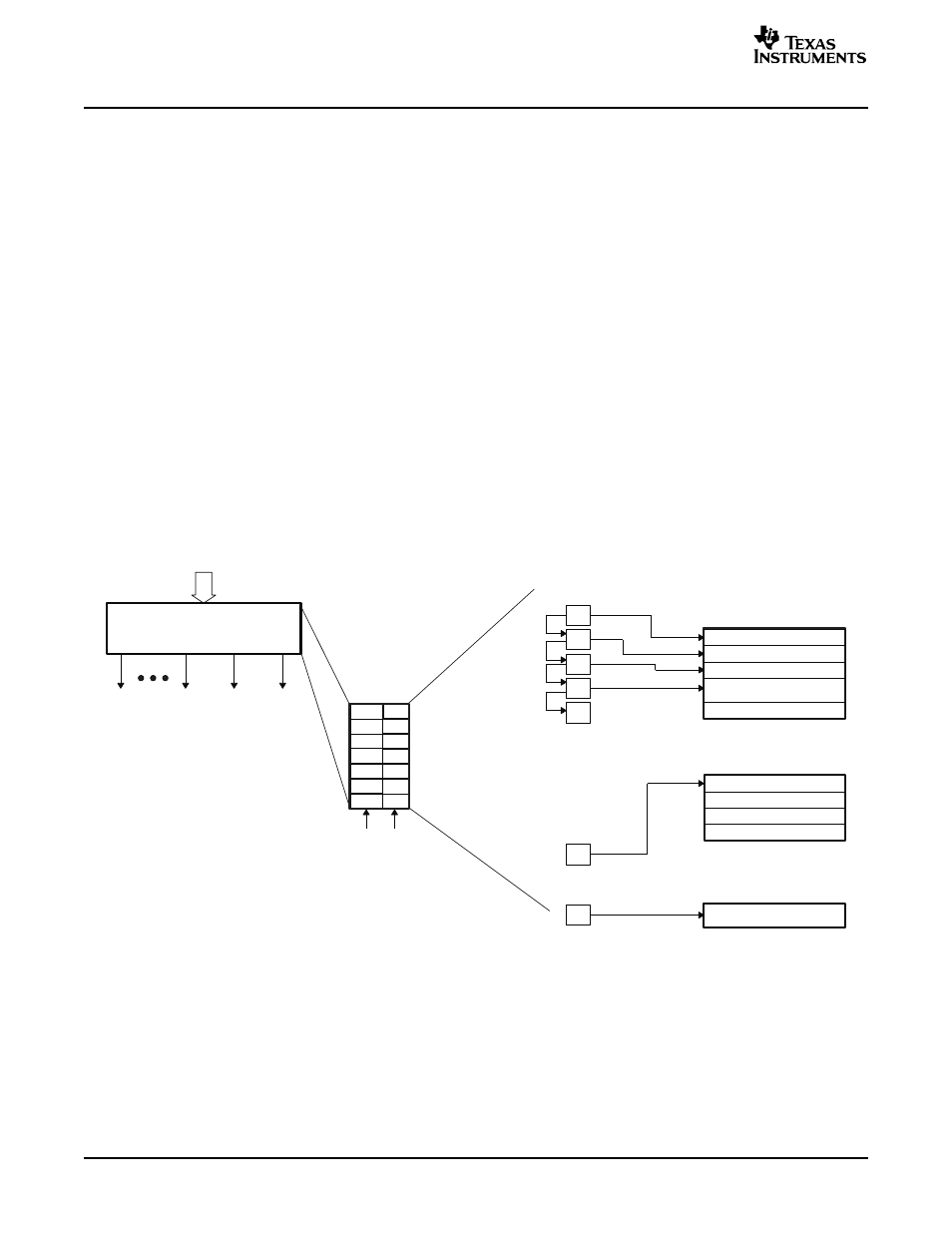

As message packets are received by the RapidIO ports, the data is written into memory while maintaining

accurate state information that is needed for future processing. For instance, if a message spans multiple

packets, information is saved that allows re-assembly of those packets by the CPU. The CPPI module

provides a scheme for tracking single and multi-packet messages, linking messages in queues, and

generating interrupts.

illustrates the scheme.

Figure 16. CPPI RX Scheme for RapidIO

Messages addressed to any of the 64 mailbox locations can be received on any of the RapidIO ports

simultaneously. Packets are handled sequentially in order of receipt. The function of the mailbox mapper

block is to direct the inbound messages to the appropriate queue and finally to the correct core. The

queue mapping is programmable and must be configured after device reset. RapidIO originally supported

only 4 mailboxes with 4 letters/mailbox. Letters allow concurrent message traffic between sender and

receiver. However, for messages that consist of only single packets, the unused 4-bit packet field normally

indicating the message segment extends the available number of mailboxes.

shows the packet

header fields for message requests.

44

Serial RapidIO (SRIO)

SPRUE13A – September 2006