Panasonic MN103001G/F01K User Manual

Page 86

Extension Instruction Specifications

3-30

Bit 31

Bit 0

MSB

LSB

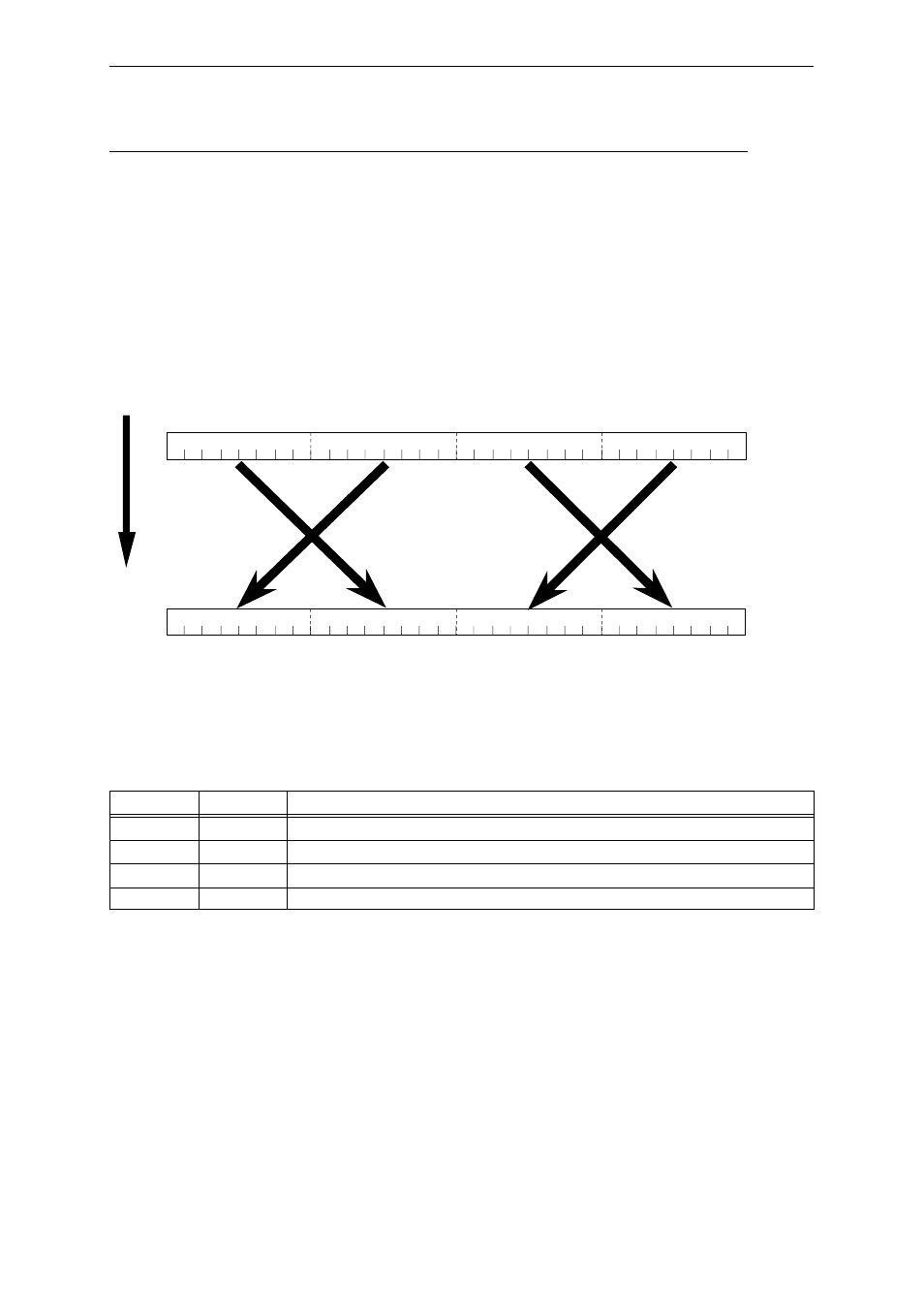

Dm before execution

Dn after execution

Dm[31:24]

Dm[23:16]

Dm[15:8]

Dm[7:0]

Bit 31

Bit 0

MSB

LSB

Dm[7:0]

Dm[15:8]

Dm[23:16]

Dm[31:24]

SWAPH (Data swapping instruction [high-order to low-order and vice versa] in two-byte data)

[Instruction Format (Macro Name)]

SWAPH

Dm, Dn

[Assembler Mnemonic]

udf09

Dm, Dn

[Operation]

This instruction swaps bits 15 through 8 of Dm with bits 7 through 0, and bits 31 through 24 with bits 23 through

16, and then stores the result in Dn.

The sample of execution

Before execution:

0x12345678

After execution:

0x34127856

[Flag Changes]

Flag

Change

Condition

V

*

Undefined

C

*

Undefined

N

*

Undefined

Z

*

Undefined

[Programming Cautions]

PSW updating by flag changes is delayed by one instruction.

However, Bcc and Lcc instructions can evaluate flags without waiting for flag reflection to PSW.

The operations of "udf09 imm8, Dn", "udf09 imm16, Dn" and "udf09 imm32, Dn" are not assured. In addition, a

system error interrupt does not occur in these cases.