Panasonic MN103001G/F01K User Manual

Page 235

8-bit Timers

10-15

When using 1/8 IOCLK or 1/32 IOCLK, the prescaler control register (TMPSCNT) must be set.

When TMnIO pin input was selected, the rising edge of the pin input signal is counted.

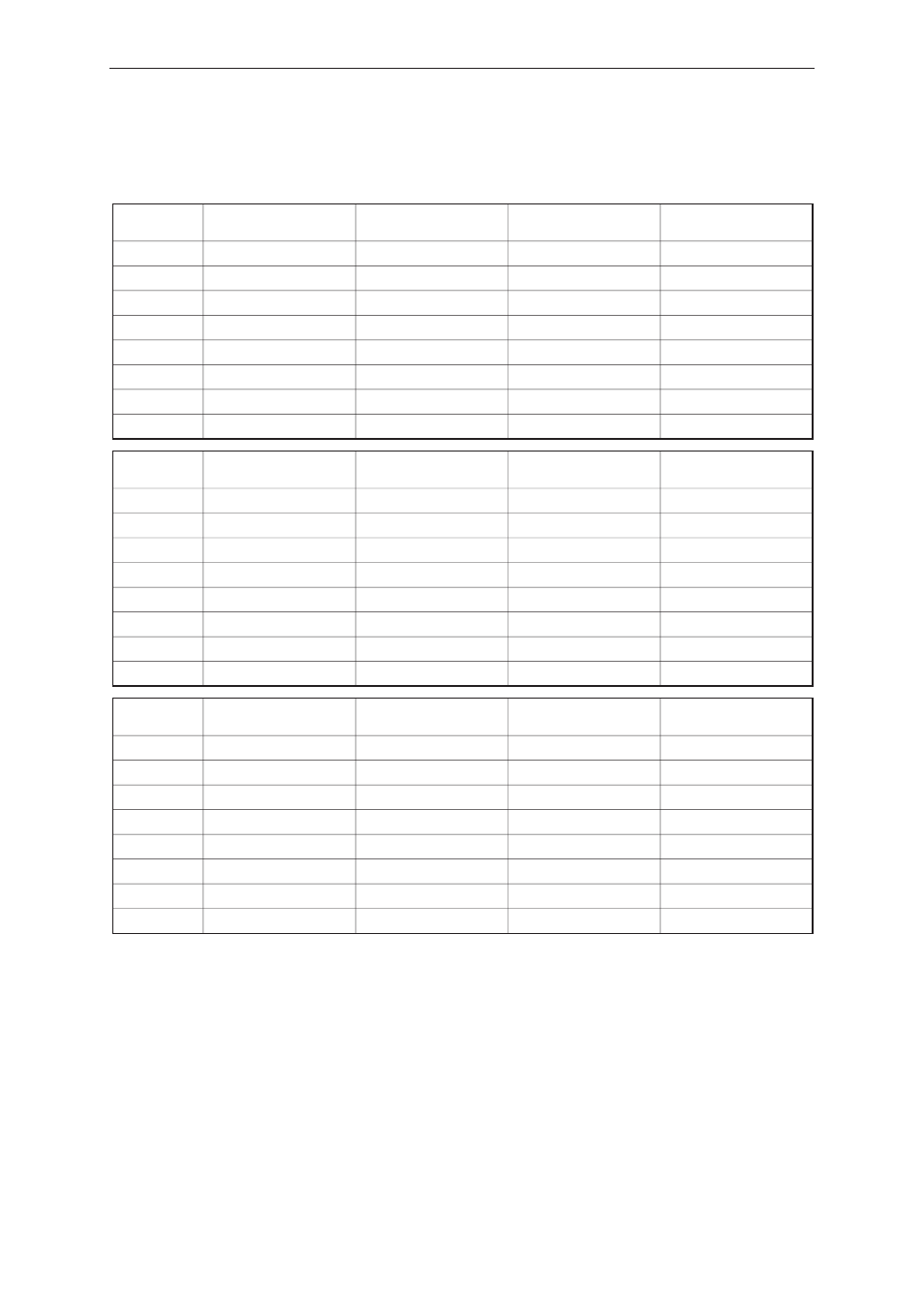

Table 10-5-3

8-bit Timer Clock Sources

TMnCK[2:0]

Setting

Timer 0

000

001

010

011

IOCLK

Timer 1

Timer 2

Timer 3

IOCLK

IOCLK

Cascaded with timer 1

IOCLK

Cascaded with timer 2

Cascaded with timer 0

Setting prohibited

100

101

110

111

Timer 2 underflow

Timer 2 underflow

Timer 0 underflow

Timer 0 underflow

Timer 0 underflow

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/32

IOCLK/32

IOCLK/32

IOCLK/32

Setting prohibited

Timer 1 underflow

Setting prohibited

Timer 1 underflow

Timer 1 underflow

Timer 2 underflow

Setting prohibited

TM0IO pin input

TM3IO pin input

TM1IO pin input

TM2IO pin input

TMnCK[2:0]

Setting

Timer 4

000

001

010

011

IOCLK

Timer 5

Timer 6

Timer 7

IOCLK

IOCLK

Cascaded with timer 5

IOCLK

Cascaded with timer 6

Cascaded with timer 4

Setting prohibited

100

101

110

111

Timer 2 underflow

Timer 2 underflow

Timer 0 underflow

Timer 0 underflow

Timer 0 underflow

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/32

IOCLK/32

IOCLK/32

IOCLK/32

Timer 1 underflow

Timer 1 underflow

Timer 1 underflow

Timer 2 underflow

TM4IO pin input

TM7IO pin input

TM5IO pin input

TM6IO pin input

Timer 0 underflow

Timer 1 underflow

Timer 2 underflow

TMnCK[2:0]

Setting

Timer 8

000

001

010

011

IOCLK

Timer 9

Timer A

Timer B

IOCLK

IOCLK

Cascaded with timer 9

IOCLK

Cascaded with timer A

Cascaded with timer 8

Setting prohibited

100

101

110

111

Timer 3 underflow

Timer 3 underflow

Timer 0 underflow

Timer 0 underflow

Timer 0 underflow

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/8

IOCLK/32

IOCLK/32

IOCLK/32

IOCLK/32

Timer 1 underflow

Timer 1 underflow

Timer 1 underflow

Timer 3 underflow

TM0IO pin input

TM3IO pin input

TM1IO pin input

TM2IO pin input

Timer 0 underflow

Timer 1 underflow

Timer 3 underflow