Panasonic MN103001G/F01K User Manual

Page 43

2-9

CPU

CPU Mode Register (CPUM)

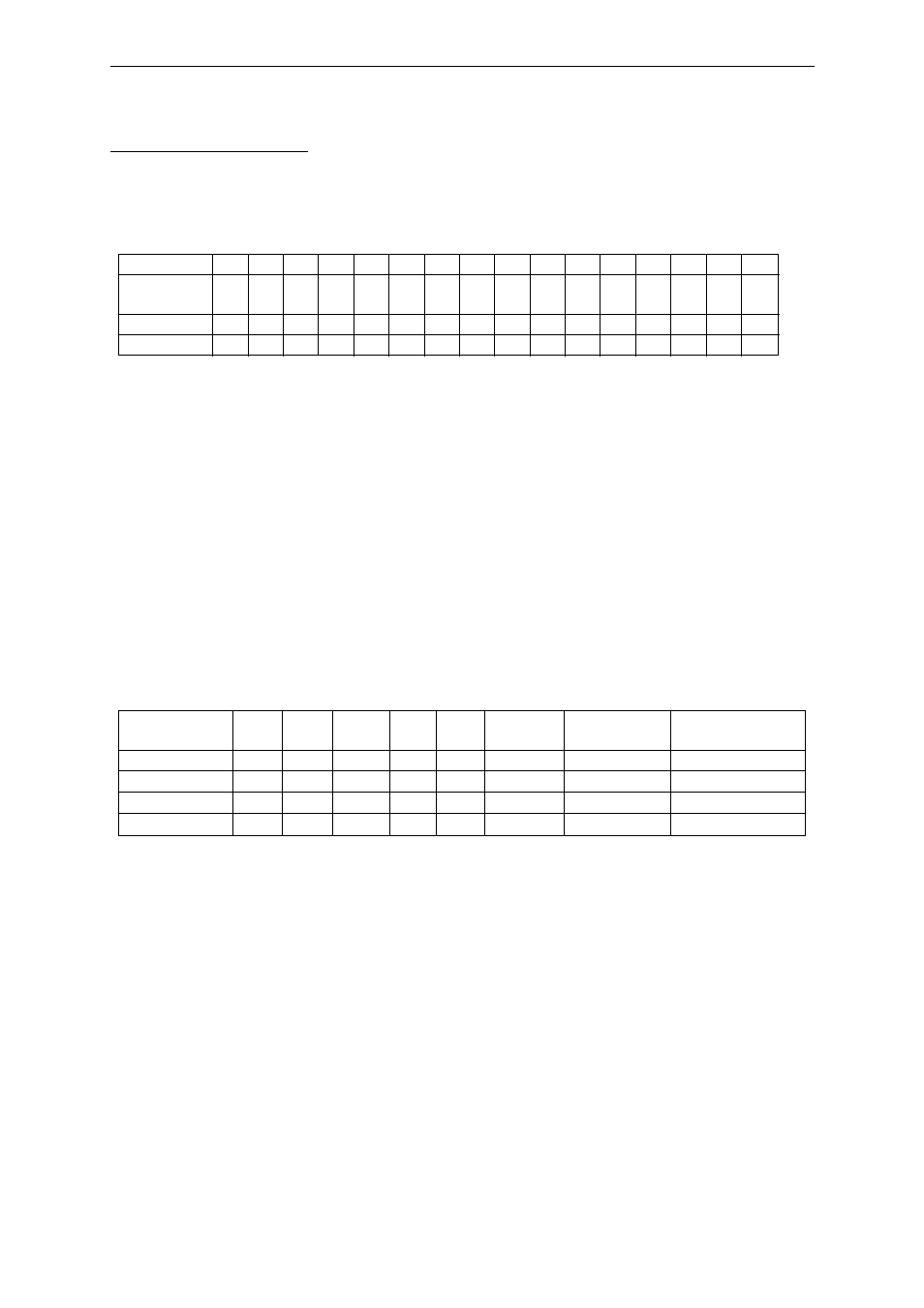

The CPU mode register (CPUM) sets the clock operating mode for the CPU and peripheral blocks. This register is

allocated to the internal I/O space at address x'20000040.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit name

—

—

—

—

—

—

—

—

—

—

OSCID STOP HALT SLEEP OSC1

OSC0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

R

R

R

R

R

R

R

R

R

R

R

R/W

R/W

R/W R/W

R/W

Bit No.

Bit name

Description

0

OSC0

Always returns "0" when read. Always write "0".

1

OSC1

Always returns "0" when read. Always write "0".

2

SLEEP

CPU operating mode control flag (SLEEP transfer request)

3

HALT

CPU operating mode control flag (HALT transfer request)

4

STOP

CPU operating mode control flag (STOP transfer request)

5

OSCID

Always returns "0" when read. Always write "0".

15 to 6

—

reserved

The various operating modes can be set by setting the bits as shown in the table below.

Oscillation control and operating mode control

Operating mode STOP HALT SLEEP OSC1 OSC0

Clock

CPU operation Peripheral function

oscillation

clock

operation clock

NORMAL

0

0

0

0

0

Oscillating

Running

Running

HALT

0

1

0

0

0

Oscillating

Stopped

Stopped

SLEEP

0

0

1

0

0

Oscillating

Stopped

Running

STOP

1

0

0

0

0

Stopped

Stopped

Stopped

The CPUM register should be accessed by halfwords (16 bits). Byte and word access is not supported.

If the CPUM register is accessed to make a transition to an operating mode of SLEEP/HALT/STOP during execution

of a program in external memory, a branch instruction should not be located within the three instructions immediately

following the CPUM register access instruction.