Panasonic MN103001G/F01K User Manual

Page 360

A/D Converter

14-6

7

ADEN

Conversion start/execution flag

(conversion can be started by writing a "1" to this flag)

0: Conversion stopped

1: Conversion start/in progress

8

ADSC0

Selection of conversion channel when converting any one channel/

indicator of current conversion channel when converting multiple channels (LSB)

9

ADSC1

Selection of conversion channel when converting any one channel/

indicator of current conversion channel when converting multiple channels (MSB)

00: AN0

01: AN1

10: AN2

11: AN3

10

—

Must be set to "0".

11

—

Must be set to "0".

12

ADMC0

Conversion channels when converting multiple channels (LSB)

13

ADMC1

Conversion channels when converting multiple channels (MSB)

00: AN0

01: AN0 to AN1

10: AN0 to AN2

11: AN0 to AN3

14

—

Must be set to "0".

15

—

Must be set to "0".

Note: When a multiple number of channels are to be converted, set "00" initially for ADSC1 to ADSC0.

A/Dn conversion data buffer (n = 0, 1, 2, 3)

Register symbol: ADnBUF

Address:

x'34000410 (n = 0), x'34000414 (n = 1), x'34000418 (n = 2), x'3400041C (n = 3)

Purpose:

This register stores the A/D conversion result for the ANn pin (channel n).

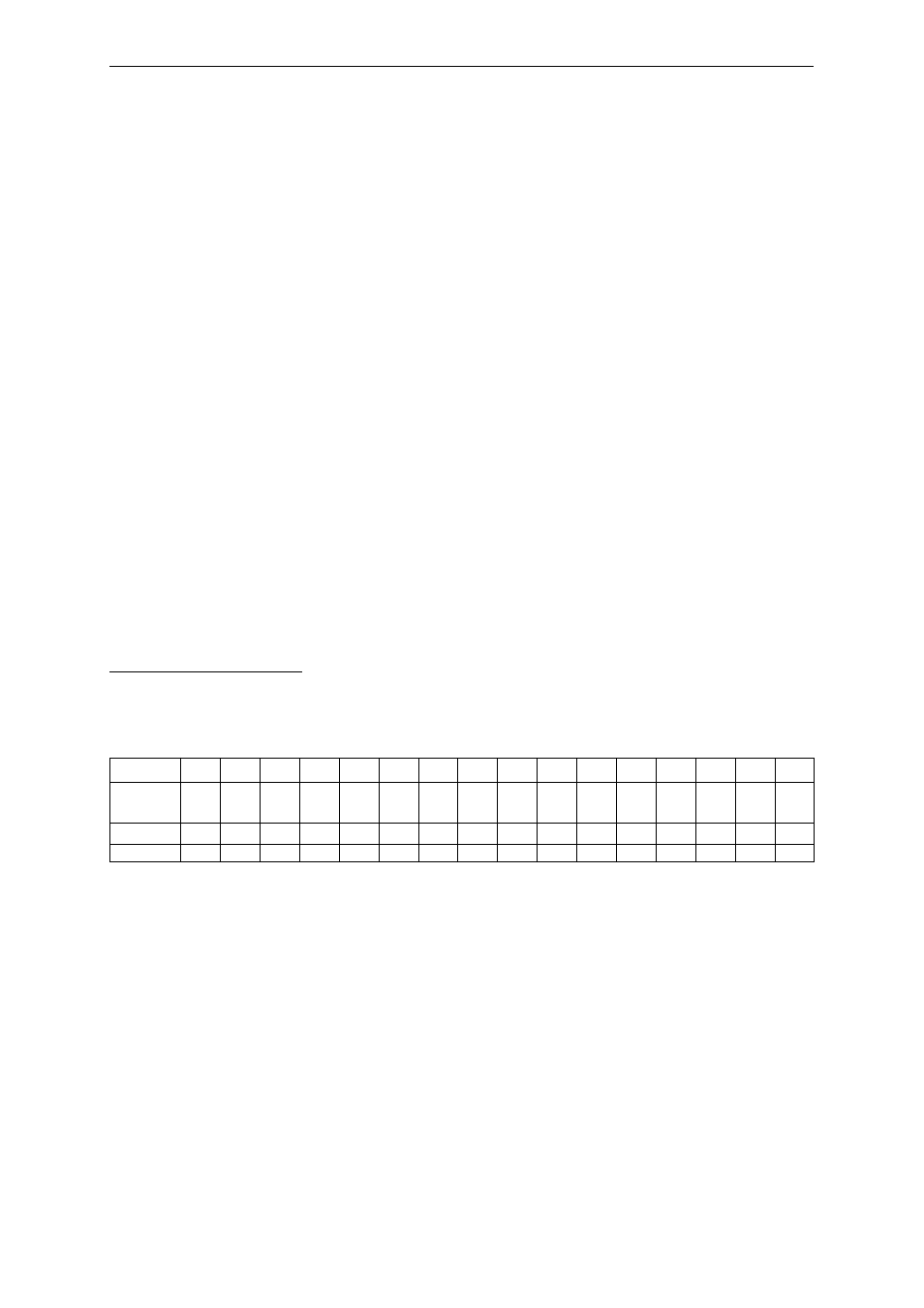

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit

ADn ADn ADn ADn ADn ADn ADn ADn ADn ADn

–

–

–

–

–

–

name

BUF15 BUF14 BUF13 BUF12 BUF11 BUF10 BUF9 BUF8 BUF7 BUF6

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

The A/D conversion result (10-bit data) is stored in bits 15 to 6.

If bits 5 to 0 are read, zeroes are returned.