Panasonic MN103001G/F01K User Manual

Page 245

8-bit Timers

10-25

[Note]

Pin input is sampled according to IOCLK. Input a signal with a pulse width of at least 6, 3, or 1.5 SYSCLK cycles

when (MCLK frequency/SYSCLK frequency) = 1, 2, or 4, respectively.

Event counting is not possible when IOCLK is stopped (in HALT or STOP mode).

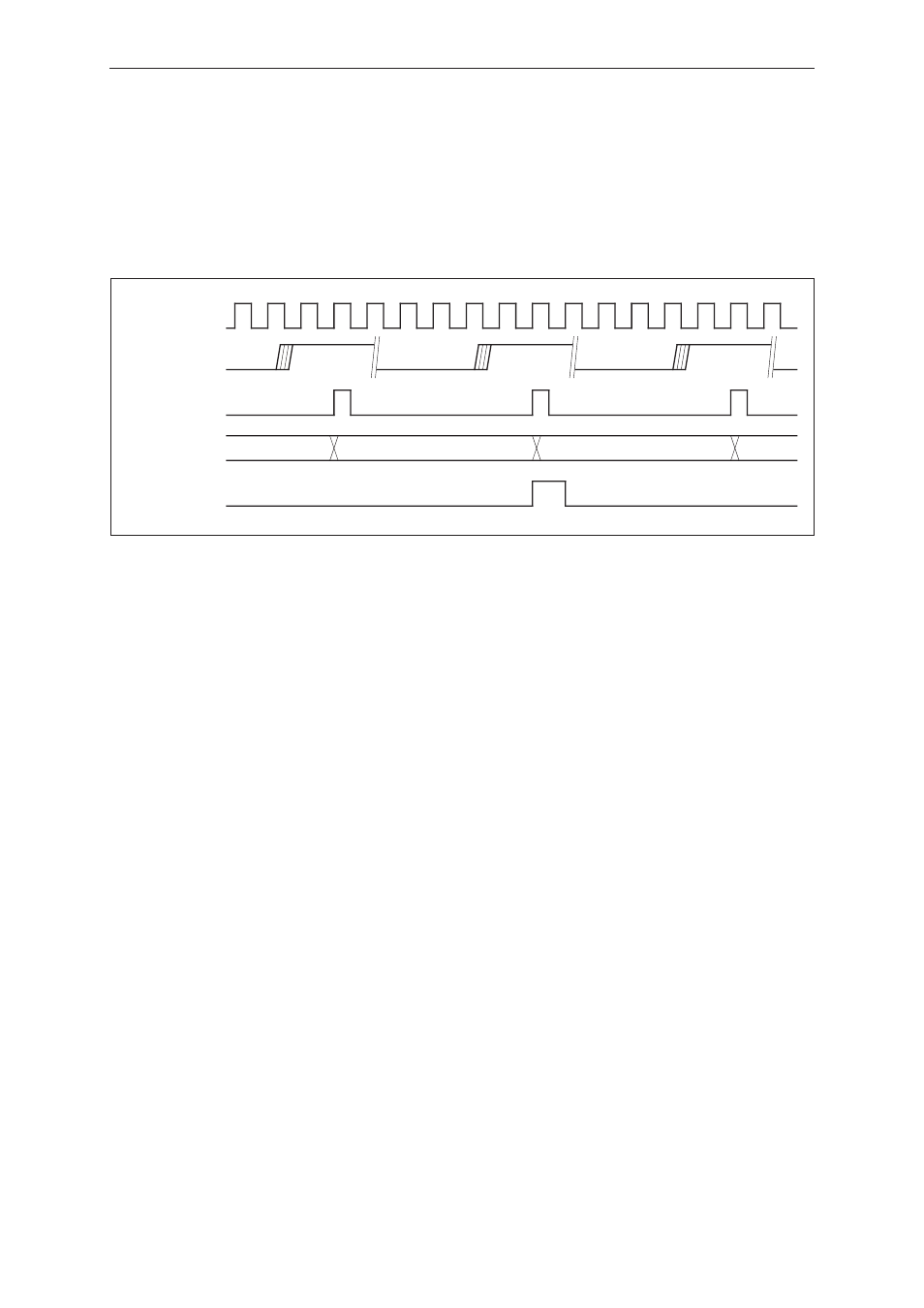

Fig. 10-6-4

Event Counting Operation

Interrupt request

signal (TMnIRQ)

TMnBC value

Count clock

x'01

IOCLK

Pin input

(TMnIO)

x'00

TMnBR value

TMnBR value-1