Panasonic MN103001G/F01K User Manual

Page 134

Bus Controller (BC)

8-20

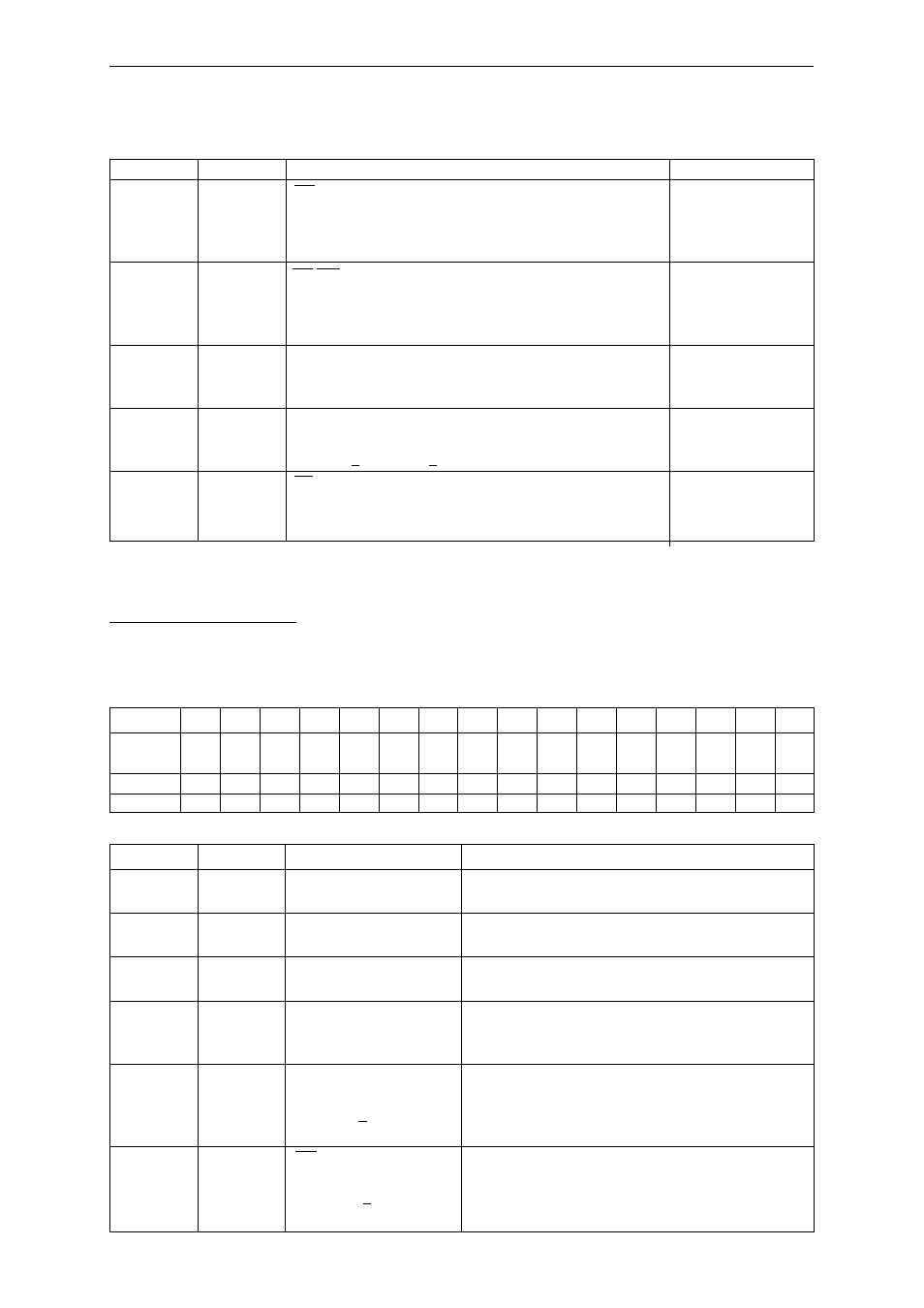

When using handshaking mode (Memory control register 3B

B3WM = 1)

Bit No.

Bit name

Description

Setting conditions

1 to 0

BCS1 to 0

DK detection wait cycle (used as parameter DW)

00: prohibited

01:

1MCLK

10:

2MCLK

11:

3MCLK

3 to 2

EA1 to 0

RE/WE assert timing

00: prohibited

01:

1MCLK

10:

2MCLK

11:

3MCLK

5 to 4

ADE1 to 0

Address output end timing

00:

0MCLK

11:

3MCLK

10 to 6

BCE4 to 0

Bus cycle end timing

00000:

0MCLK

Set so that:

BCE

≥

REN, BCE

≥

WEN

11111: 31MCLK

15 to 11

REN4 to 0

RE negate timing

00000:

0MCLK

11111: 31MCLK

Note: Handshaking mode can only be set when (MCLK frequency/SYSCLK frequency) = 4.

If (MCLK frequency/SYSCLK frequency) = 1 or 2, set B3WM = 0 in MEMCTR3B.

When using fixed wait mode (Memory control register 3B B3WM = 0)

Bit No.

Bit name

Description

Setting conditions

1

WM

Block 3 wait mode

0: fixed wait mode

2

BM

Block 3 bus mode

0: Synchronous mode (SYSCLK synchronization)

1: Asynchronous mode (MCLK synchronization)

4

BW

Block 3 bus width

0:

8 bits

1:

16 bits

7 to 6

ASA1 to 0

AS assert timing

00:

0MCLK

11:

3MCLK

10 to 8

ASN2 to 0

AS negate timing

000:

prohibited

Set so that:

001:

1MCLK

ASN

≥

ASA

111:

7MCLK

15 to 11

WEN4 to 0

WE negate timing

Settings other than those shown below are prohibited.

Set so that:

00011:

3MCLK

WEN

≥

EA

11111:

31MCLK

~

~

~

~

~

~

Memory control register 3B

Register symbol: MEMCTR3B

Address:

x’32000026

Purpose:

Sets the bus mode, access timing, etc., for external memory space block 3.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit

B3

B3

B3

B3

B3

B3

B3

B3

B3

B3

–

B3

–

B3

B3

–

name

WEN4WEN3WEN2WEN1WEN0 ASN2 ASN1 ASN0 ASA1 ASA0

BW

BM

WM

Reset

1

1

1

0

1

0

1

1

0

1

0

1

0

0

0

0

Access

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R/W

R

R/W

R/W

R

~

~

~

~

~

~