Panasonic MN103001G/F01K User Manual

Page 198

Interrupt Controller

9-10

Group 2 interrupt control register

Register symbol: G2ICR

Address:

x'34000108

Purpose:

This register is used to enable group 2 interrupts, and to confirm interrupt requests and detection.

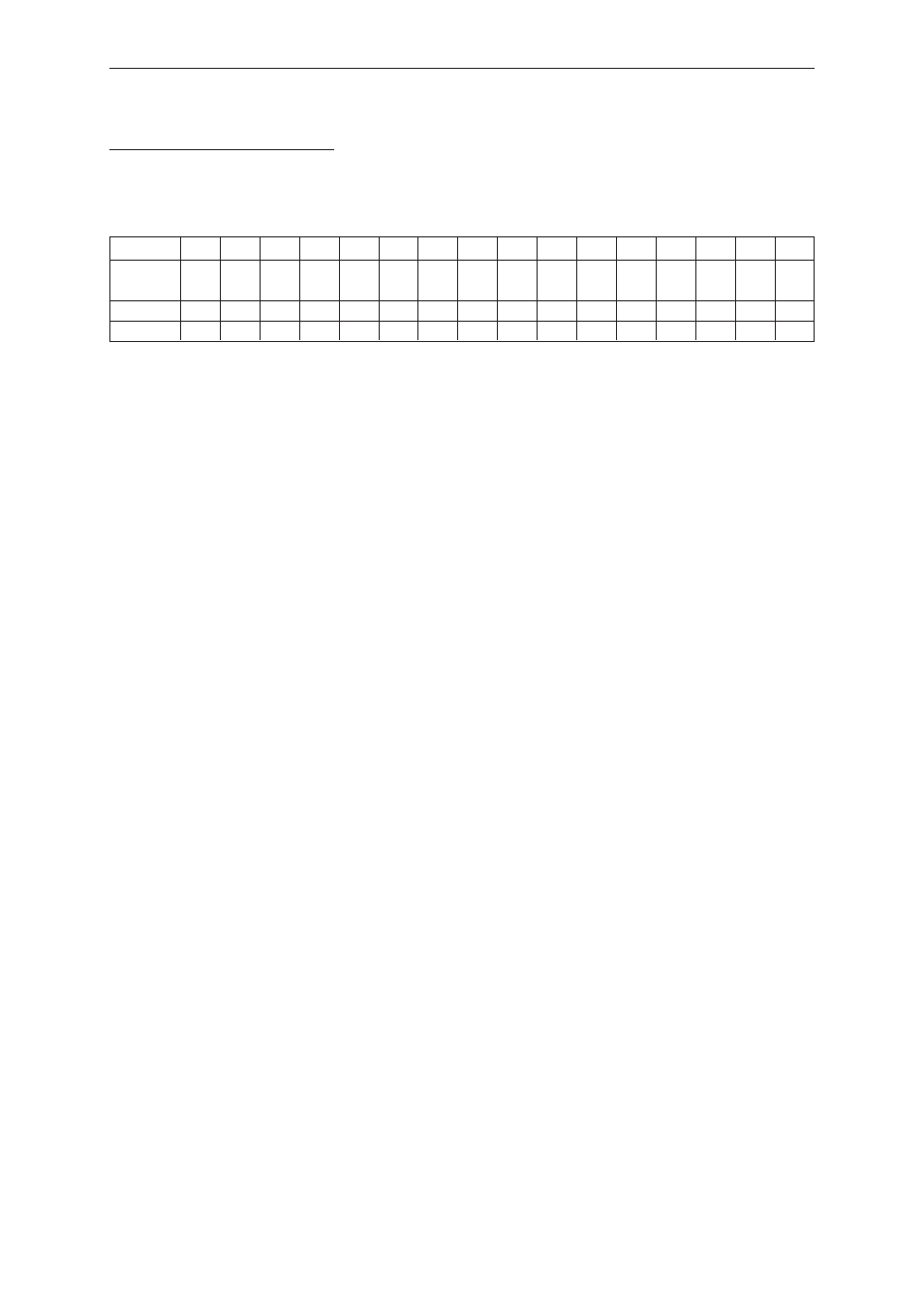

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit

-

G2

G2

G2

TM3 TM2 TM1 TM0 TM3 TM2 TM1 TM0 TM3 TM2 TM1 TM0

name

LV2

LV1

LV0

IE

IE

IE

IE

IR

IR

IR

IR

ID

ID

ID

ID

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit No.

Bit name

Description

0

TM0ID

Timer 0 underflow interrupt detection flag

0: No interrupt detected

1: Interrupt detected

1

TM1ID

Timer 1 underflow interrupt detection flag

0: No interrupt detected

1: Interrupt detected

2

TM2ID

Timer 2 underflow interrupt detection flag

0: No interrupt detected

1: Interrupt detected

3

TM3ID

Timer 3 underflow interrupt detection flag

0: No interrupt detected

1: Interrupt detected

4

TM0IR

Timer 0 underflow interrupt request flag

0: No interrupt request

1: Interrupt request

5

TM1IR

Timer 1 underflow interrupt request flag

0: No interrupt request

1: Interrupt request

6

TM2IR

Timer 2 underflow interrupt request flag

0: No interrupt request

1: Interrupt request

7

TM3IR

Timer 3 underflow interrupt request flag

0: No interrupt request

1: Interrupt request

8

TM0IE

Timer 0 underflow interrupt enable flag

0: Disabled

1: Enabled

9

TM1IE

Timer 1 underflow interrupt enable flag

0: Disabled

1: Enabled

10

TM2IE

Timer 2 underflow interrupt enable flag

0: Disabled

1: Enabled

11

TM3IE

Timer 3 underflow interrupt enable flag

0: Disabled

1: Enabled

12

G2LV0

Group 2 interrupt priority level register (LSB)

13

G2LV1

Group 2 interrupt priority level register

14

G2LV2

Group 2 interrupt priority level register (MSB)

Set a level from 6 to 0.

15

—

"0" is returned when this bit is read.