Panasonic MN103001G/F01K User Manual

Page 54

2-20

CPU

(Example of pre-processing by the interrupt handler)

1.

The registers are saved.

The saved registers are those used by the interrupt handler.

2.

The interrupt group analysis is executed.

2.1 The interrupt acknowledge sequence is executed.

Interrupt acknowledge consists of reading out the interrupt accept group register (IAGR) to obtain the group

number of the interrupt group with the highest priority among the specified interrupt levels.

2.2 The leading address of the interrupt handler for each level is generated.

2.3 Control is transferred to the interrupt handler for each level.

3.

When there are multiple factors within the same group, the interrupt control register (GnICR) is read out to

designate the factor.

* In case of non-maskable interrupts, the factor is specified by accessing the NMICR directly without accessing

the IAGR.

4.

Control is transferred to the interrupt handler for each factor.

Note that because this microcontroller uses a store buffer when writing data via the bus controller, it is necessary,

when releasing the interrupt factor, to read the appropriate register immediately after clearing the interrupt

factor in order to wait for the factor in the GnICR to be cleared completely.

(Example of post-processing by the interrupt handler)

5.

The registers are restored.

The restored registers are those saved by the pre-processing.

6.

The RTI instruction is executed and control returns to the program before the interrupt.

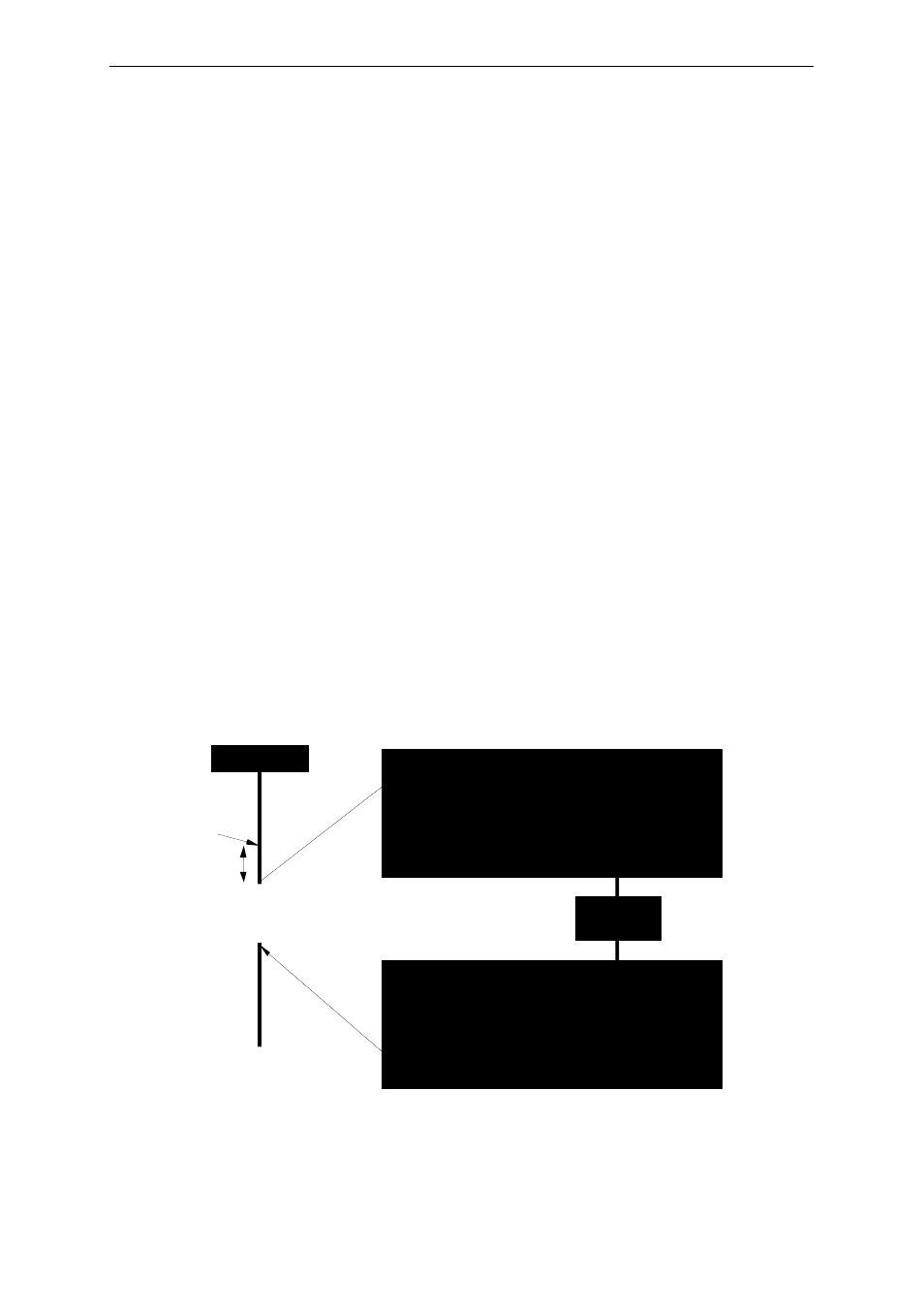

Fig. 2-5-5 shows the interrupt sequence flow. (when not accepting nested interrupts)

The numbers in the figure correspond to the numbers of processing performed by the interrupt handler in the

previous section.

Fig. 2-5-5 Interrupt Sequence Flow

Interrupt processing

and interrupt request

cancel

Program

Handler (pre-processing)

Interrupt

max. 11 Cycles

Interrupt processing by hardware

RTI

Interrupt

handler

Handler (post-processing)

1

2

3

4

5

6

Processing for each level

Processing for each group

Processing for

each factor

3 Cycles