Panasonic MN103001G/F01K User Manual

Page 217

Interrupt Controller

9-29

External interrupt condition specification register

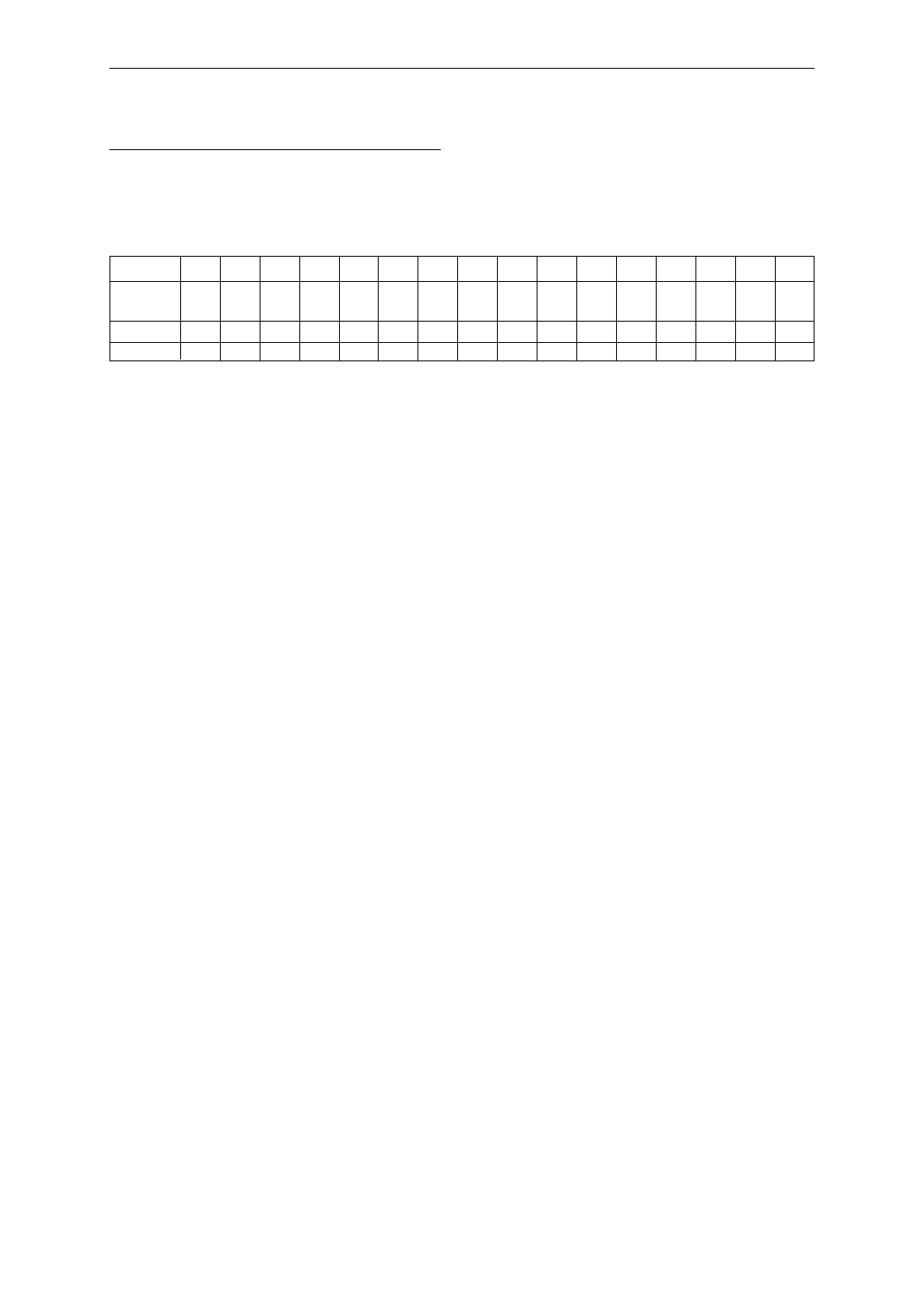

Register symbol: EXTMD

Address:

x'34000280

Purpose:

This register specifies the external interrupt generation conditions. Set the desired level or

edge for each pin.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit

IR7

IR7

IR6

IR6

IR5

IR5

IR4

IR4

IR3

IR3

IR2

IR2

IR1

IR1

IR0

IR0

name

TG1

TG0

TG1

TG0

TG1

TG0

TG1

TG0

TG1

TG0

TG1

TG0

TG1

TG0

TG1

TG0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit No.

Bit name

Description

0

IR0TG0

IRQ0 pin trigger condition setting (LSB)

1

IR0TG1

IRQ0 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

2

IR1TG0

IRQ1 pin trigger condition setting (LSB)

3

IR1TG1

IRQ1 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

4

IR2TG0

IRQ2 pin trigger condition setting (LSB)

5

IR2TG1

IRQ2 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

6

IR3TG0

IRQ3 pin trigger condition setting (LSB)

7

IR3TG1

IRQ3 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

8

IR4TG0

IRQ4 pin trigger condition setting (LSB)

9

IR4TG1

IRQ4 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

10

IR5TG0

IRQ5 pin trigger condition setting (LSB)

11

IR5TG1

IRQ5 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

12

IR6TG0

IRQ6 pin trigger condition setting (LSB)

13

IR6TG1

IRQ6 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

14

IR7TG0

IRQ7 pin trigger condition setting (LSB)

15

IR7TG1

IRQ7 pin trigger condition setting (MSB)

00: Positive edge

01: Negative edge

10: "H" level

11: "L" level

Note : Change the conditions under which the external interrupt is triggered while the IE bit of the interrupt control

register GnICR (n=11 to 18) for each of the groups 11 to 18 is not set to "1" (interrupt enable).