Panasonic MN103001G/F01K User Manual

Page 42

2-8

CPU

Interrupt Vector Register (IVARn)

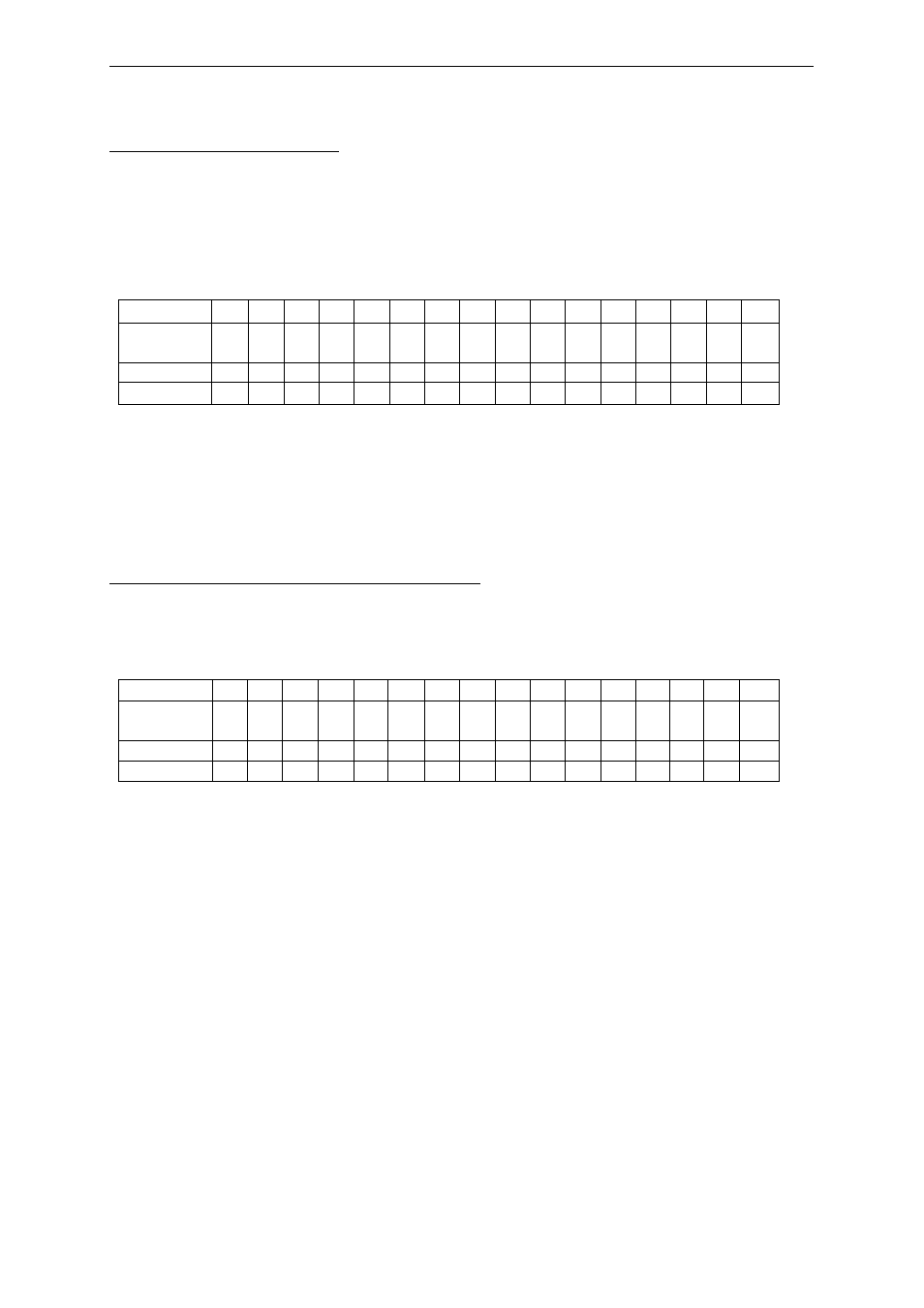

The interrupt vector register (IVAR0 to IVAR6) contains the lower 16 bits of the start address of the interrupt

handler for interrupts of the level accepted by the CPU. IVAR0 corresponds to level 0 interrupts; in similar fashion,

IVAR1 to IVAR6 correspond to levels 1 to 6, respectively. IVAR0 to IVAR6 are allocated to the internal I/O space

between addresses x'20000000 to x'20000018, respectively.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit name

IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR IVAR

n15

n14

n13

n12

n11

n10

n9

n8

n7

n6

n5

n4

n3

n2

n1

n0

Reset

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

Access

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit No.

Bit name

Description

15 to 0

IVARn15 to 0

Lower 16 bits of the start address of the level interrupt handler

The IVARn register should be accessed by halfwords (16 bits). Byte and word access is not supported.

Note that the upper 16 bits of the start address of the level interrupt handler are fixed to x'4000.

Core's Internal Memory Control Register (MEMCTRC)

The core's internal memory control register (MEMCTRC) sets the number of waits for the memory mounted inside

this microcontroller. This register is allocated to the internal I/O space at address x'20000020.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit name

—

—

—

—

—

—

—

—

—

—

—

—

LD

EXT DROM ROM

USE

WAIT

W

WAIT

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

Access

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

Writing these bits is prohibited, since operation is guaranteed only with the settings that are in place after a reset.

(n = 0, 1, 2, 3, 4, 5, 6)