Panasonic MN103001G/F01K User Manual

Page 219

Interrupt Controller

9-31

[Cautions]

1.

Maintain external pin interrupt signals for at least 10, 5, or 2.5 SYSCLK cycles when

n

fr = (MCLK frequency/

SYSCLK frequency) = 1, 2, or 4, respectively. The interrupt cannot be detected if the signal is not maintained

for at least that long.

However, when recovering from HALT mode in response to an external pin interrupt signal, maintain the

signal for at least 22, 11, or 5.5 SYSCLK cycles when

n

fr = 1, 2, or 4, respectively. Furthermore, when

recovering from STOP mode in response to an external pin interrupt signal, maintain the signal for at least 10,

5, 2.5 SYSCLK cycles when

n

fr = 1, 2, or 4, respectively, if there is just one interrupt factor; if there are

multiple interrupt factors, continue the external pin interrupt request until the interrupt factors are confirmed by

the interrupt processing program.

2

Although it is possible to recover from STOP, HALT, or SLEEP mode in response to an external pin (IRQ7 to

0) interrupt, the trigger conditions for recovery differ for each mode, as indicated in the table below.

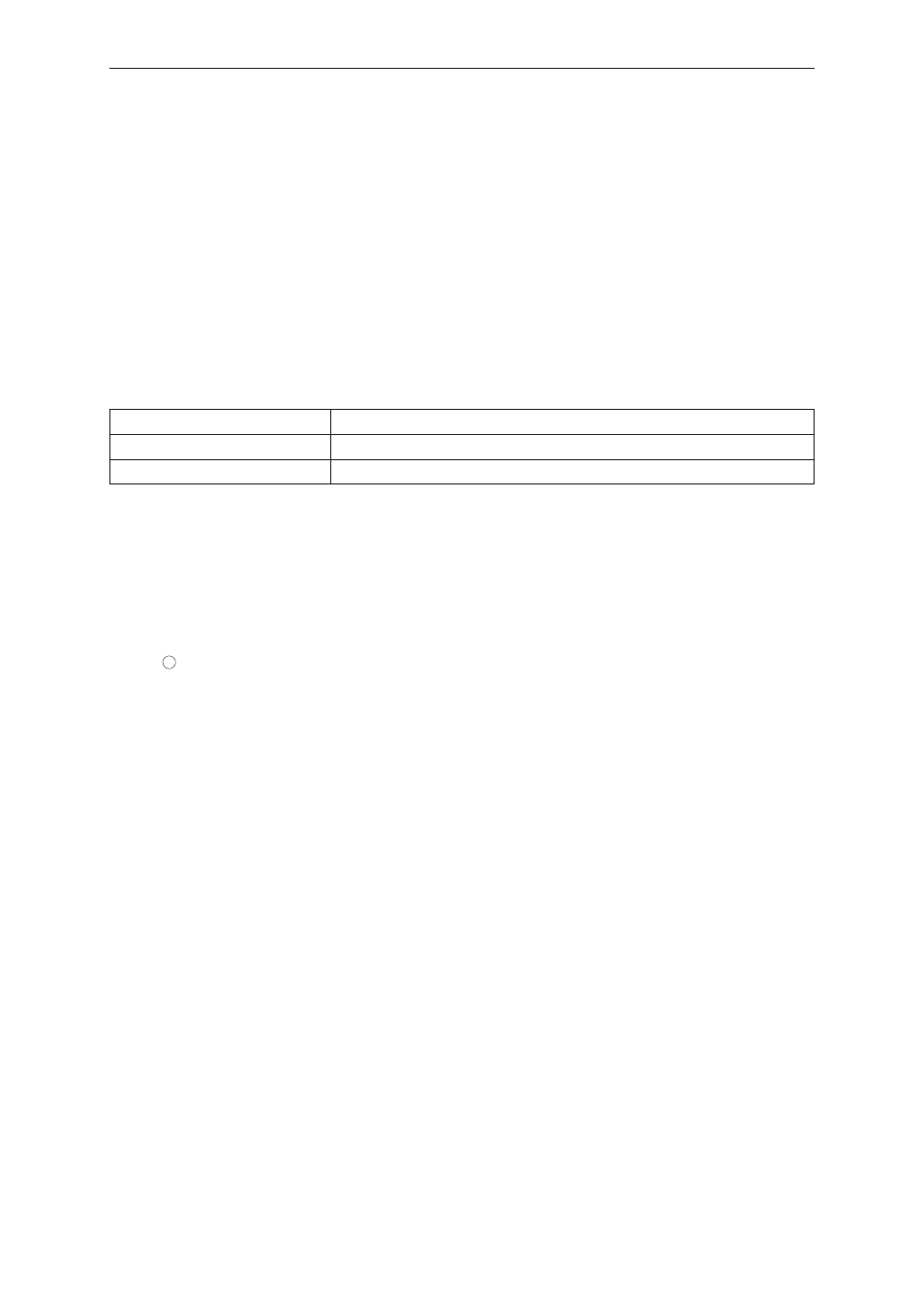

Mode

Trigger conditions for recovery

STOP or HALT mode

"H"/"L" level (recovery in response to edge input is not possible)

SLEEP mode

Positive edge/negative edge/"H" level/"L" level

3

When writing a GnICR register in an interrupt program in order to clear IR and ID and then returning from the

interrupt program, in order to gain synchronization with the bus controller store buffer be certain to perform an

I/O bus access between the execution of the instruction (movbu, etc.) that is used to write the clear data to the

GnICR register and the execution of the instruction to return from the interrupt program.

Example:

After clearing a GnICR register, read it again.

mov

0x0f:b,d0

; (d0 = clear data)

movbu d0,(GnICR)

; Clears the GnICR flags (GnICR = address of GnICR register to be cleared)

movhu (GnICR),d1

; I/O bus access

(Reads the GnICR register that was cleared)

rti

; Instruction to return from interrupt program

If there is no I/O bus access between the instruction that is used to write the clear data to the GnICR register and

the instruction to return from the interrupt program, the return from the interrupt program is not guaranteed.

Misoperation will occur when executing the interrupt program again after returning, especially when the

RETURN instruction is described after a clear data write.

x

mov

0x0f:b,d0

;

movbu d0,(GnICR)

; Clears the GnICR flags

rti

; Instruction to return from interrupt program