Panasonic MN103001G/F01K User Manual

Page 233

8-bit Timers

10-13

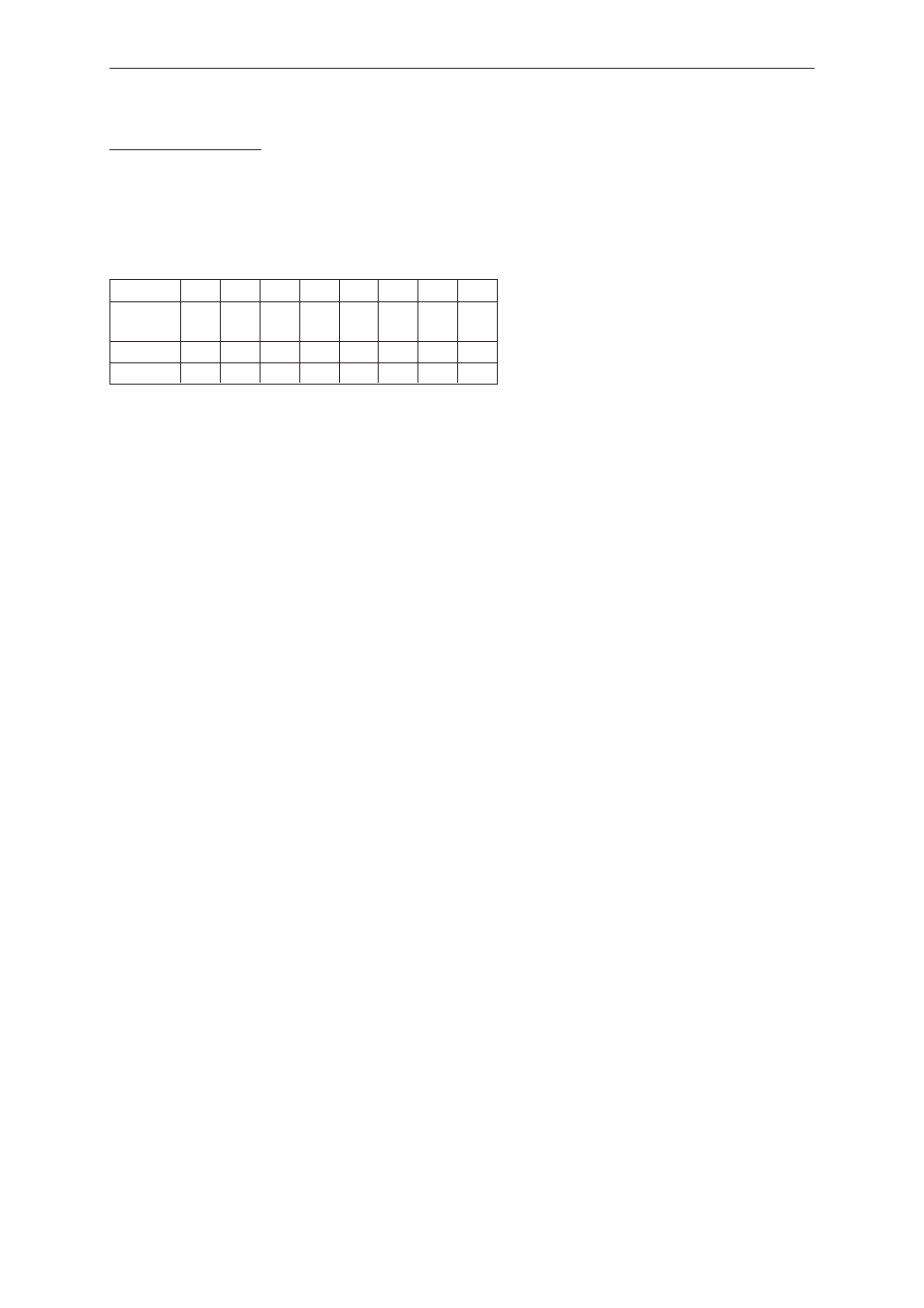

Timer n mode register (n = 4, 5, 6, 7, 8, 9, A, B)

Register symbol: TMnMD

Address:

x'34001004 (n=4), x'34001005 (n=5), x'34001006 (n=6),

x'34001007 (n=7), x'34001008 (n=8), x'34001009 (n=9),

x'3400100A (n=A), x'3400100B (n=B)

Purpose:

This register controls the operation of timer n.

Bit No.

7

6

5

4

3

2

1

0

Bit

TMn TMn TMn TMn

-

TMn TMn TMn

name

CNE LDE OM1 OM0

CK2

CK1

CK0

Reset

0

0

0

0

0

0

0

0

Access

R/W

R/W

R/W

R/W

R

R/W

R/W

R/W

Bit No.

Bit name

Description

0

TMnCK0

Timer n clock source selection flag (LSB)

1

TMnCK1

Timer n clock source selection flag

2

TMnCK2

Timer n clock source selection flag (MSB)

These bits select the timer clock source.

When pin input is selected, the rising edge of the pin input signal is counted.

For details on each timer clock sources, refer to Table 10-5-3, "8-bit Timer Clock

Sources."

3

—

"0" is returned when this bit is read.

4

TMnOM0

Timer n output mode flag (LSB)

5

TMnOM1

Timer n output mode flag (MSB)

These bits select the timer n output waveform.

For details on each PWM output waveform, refer to Table 10-5-2, "PWM Output

Waves."

00: Underflow 1/2 cycle output ("L" level output during timer n initialization)

01: Underflow 1/2 cycle output ("H" level output during timer n initialization)

10: PWM output ("L" level output during timer n initialization)

11: PWM output ("H" level output during timer n initialization)

6

TMnLDE

Timer n initialization flag

Initializes timer n.

0: Normal operation

1: Initialization

Loads the value in TMnBR into TMnBC.

Resets timer output n.

Loads the value in the compare register buffer into the compare register.

7

TMnCNE

Timer n operation enable flag

Enables/disables the timer n count operation.

0: Operation disabled

1: Operation enabled