4 description of registers, 5 14.4 description of registers – Panasonic MN103001G/F01K User Manual

Page 359

A/D Converter

14-5

14.4 Description of Registers

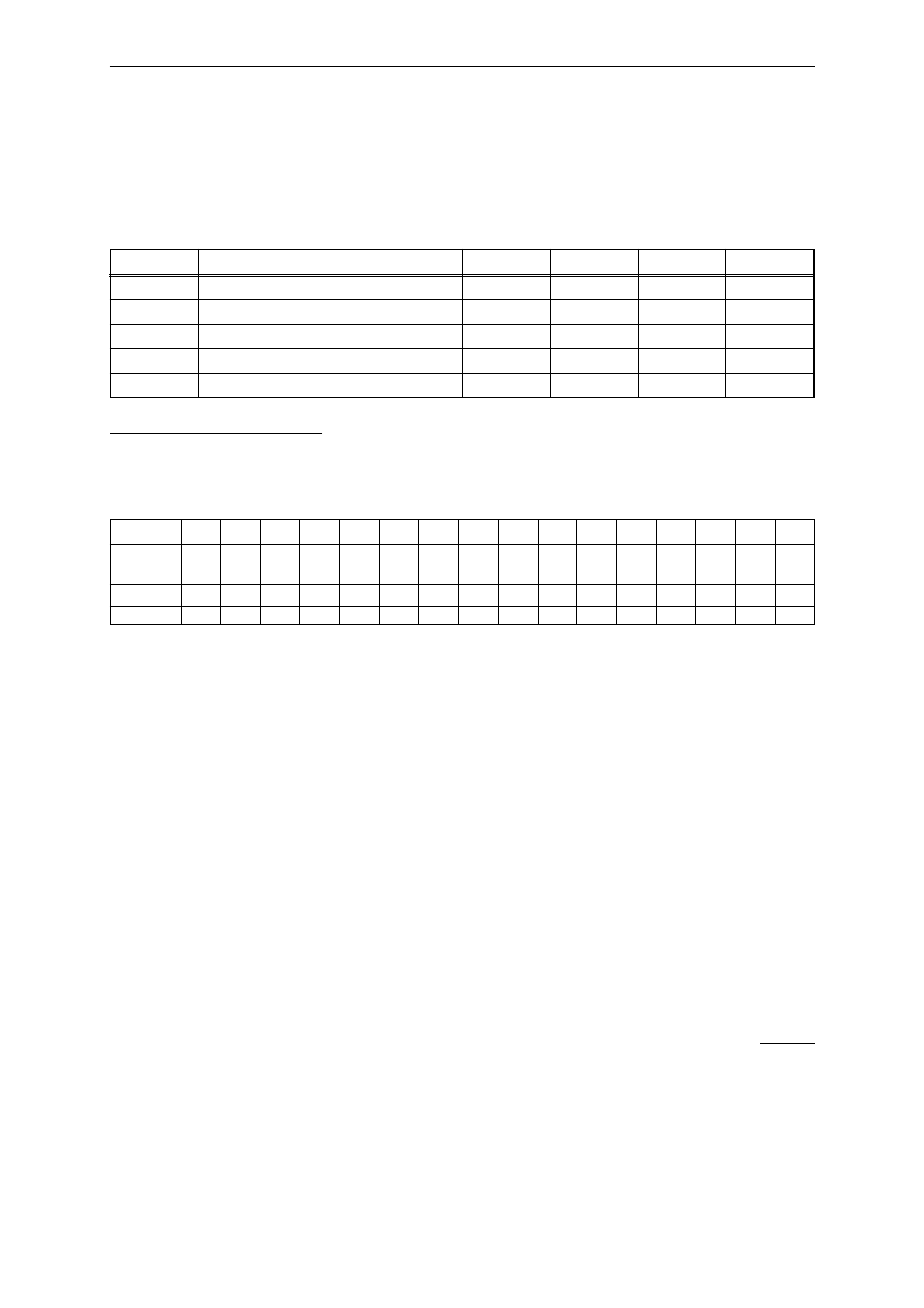

Table 14-4-1 lists the registers for this A/D converter.

Table 14-4-1 A/D Register List

Address

Name

Symbol

Number of bits Initial value Access size

x'34000400

A/D conversion control register

ADCTR

16

x'0000

8, 16

x'34000410

A/D0 conversion data buffer

AD0BUF

16

x'0000

8, 16

x'34000414

A/D1 conversion data buffer

AD1BUF

16

x'0000

8, 16

x'34000418

A/D2 conversion data buffer

AD2BUF

16

x'0000

8, 16

x'3400041C A/D3 conversion data buffer

AD3BUF

16

x'0000

8, 16

A/D conversion control register

Register symbol: ADCTR

Address:

x'34000400

Purpose:

This register sets the A/D conversion operation control conditions.

Bit No.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Bit

–

–

AD

AD

–

–

AD

AD

AD

AD

AD

AD

AD

AD

AD

AD

name

MC1 MC0

SC1

SC0

EN

ST1

ST0

SHC

CK1

CK0 MD1 MD0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Bit No.

Bit name

Description

0

ADMD0

Operating mode selection (LSB)

1

ADMD1

Operating mode selection (MSB)

00: Any one channel/one-time conversion

01: Multiple channels/one-time conversion

10: Any one channel/continuous conversion

11: Multiple channels/continuous conversion

2

ADCK0

Conversion reference clock selection (LSB)

3

ADCK1

Conversion reference clock selection (MSB)

00: IOCLK/2

01: IOCLK/4

10: IOCLK/8

11: IOCLK/16

4

ADSHC

Sampling cycle number selection

0: Two conversion reference clock cycles

1: Four conversion reference clock cycles

5

ADST0

Conversion start trigger selection (LSB)

6

ADST1

Conversion start trigger selection (MSB)

00: Conversion start by software

01: External trigger (ADEN flag is set by input of falling edge to ADTRG

pin)

10: Timer trigger (ADEN flag is set by timer 2 underflow)

11: Setting prohibited