Paradyne 9128-II User Manual

Page 95

3. Configuration

9128-A2-GB20-60

April 2002

3-61

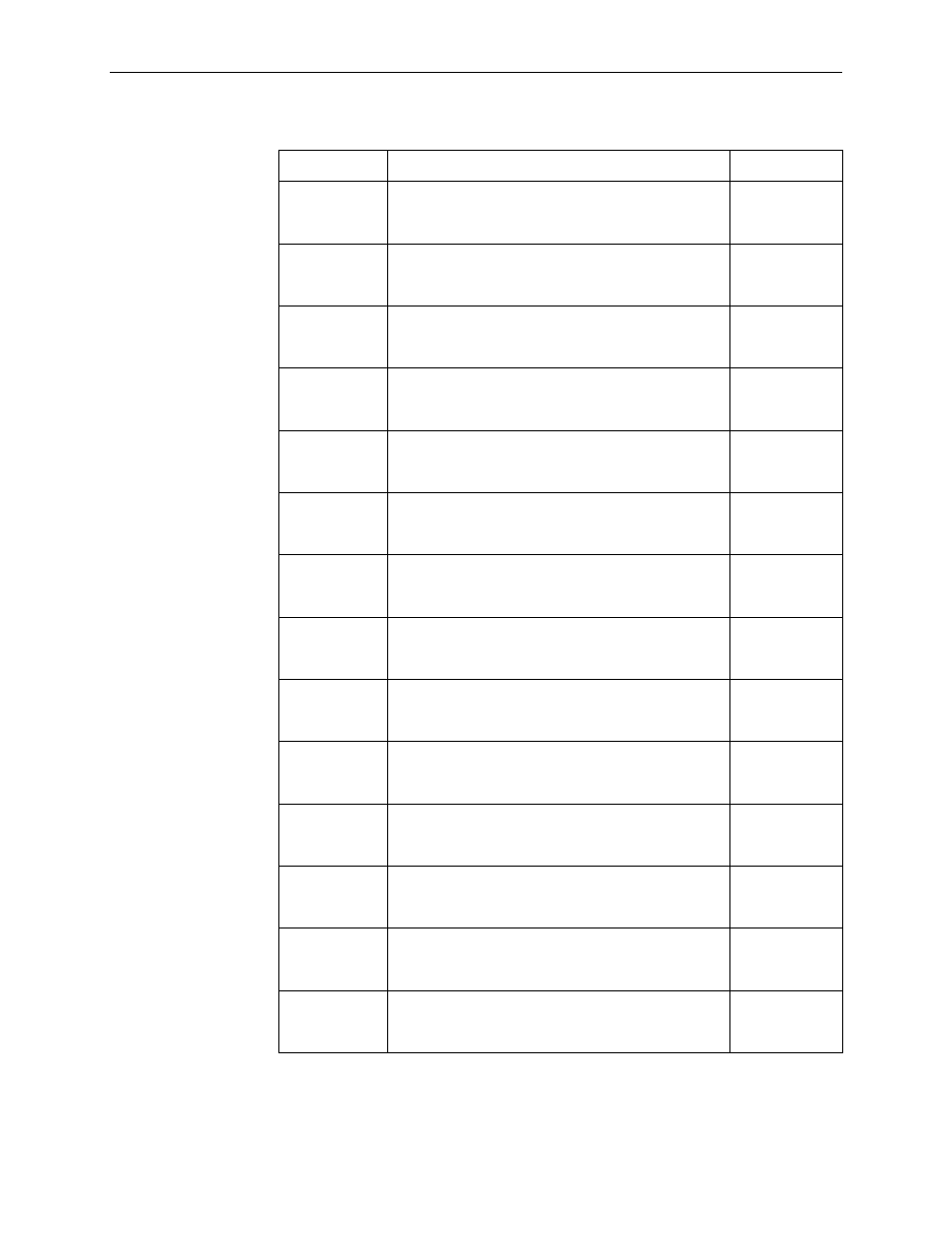

E&M-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an E&M interface (ABCD = 0000).

E&M idle

E&M-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an E&M interface (ABCD = 1111).

E&M busy

FXOg-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXO Ground-Start interface (ABCD = 1111).

FXSg-idle

FXOg-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXO Ground-Start interface (ABCD = 0101).

FXSg-busy

FXOl-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXO Loop-Start interface (ABCD = 0101).

FXSl-idle

FXOl-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXO Loop-Start interface (ABCD = 0101).

FXSl-busy

FXSg-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXS Ground-Start interface (ABCD = 0101).

FXOg-idle

FXSg-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXS Ground-Start interface (ABCD = 1111).

FXOg-busy

FXSl-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXS Loop-Start interface (ABCD = 0101).

FXOl-idle

FXSl-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXS Loop-Start interface (ABCD = 1111).

FXOl-busy

FXOD-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXODN interface (ABCD = 0000).

FXSD-idle

FXOD-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXODN interface (ABCD = 1111).

FXSD-busy

FXSD-idle

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the idle state for

an FXSDN interface (ABCD = 0000).

FXOD-idle

FXSD-busy

The signaling bits transmitted to the cross-connected

T1 interface during a CGA represent the busy state

for an FXSDN interface (ABCD = 1111).

FXOD-busy

Table 3-12. Signaling and Trunk Conditioning Values (2 of 3)

Network Side

Meanings

DSX-1 Side