Trace interface, Jtag interface, Debugging via uart – Siemens ERTEC200 User Manual

Page 95: Test and debugging, Etm9 embedded trace macrocell, Trace modes, Features of the etm9 module, Etm9 registers

11.2 Trace Interface

The trace interface is parameterized, enabled, and disabled by means of a connected debugger (e.g. by Lauterbach) on

the JTAG interface.

A Trace port is provided in the ERTEC 200 for tracing internal processor states:

• PIPESTA

[2:0]

• TRACESYNC

• TRACECLK

• TRACEPKT[7:0]

The PIPESTA[2:0], TRACEPKT[7:0], and TRACESYNC signals are alternative signal pins at the LBU interface. The

trace interface is activated with the configuration pins CONFIG[6,5,2] = 101. The trace interface can be assigned

parameters in the debugger with 4-bit or 8-bit data width. If a data width of 4 bits is assigned, the TRACEPKT[3:0] signals

are automatically switched to trace function. If a data width of 8 bits is assigned, the TRACEPKT[7:4] signals are also

switched to trace function.

For connectors, pinning, and hardware circuitry for the Trace interface, refer to /7/.

11.3 JTAG Interface

Besides the debug function, the JTAG interface is also used for the boundary scan (see /9/). In addition to the JTAG

interface, the DBGREQ and DBGACK signals are available as alternative function pins for debugging. Due to the

different debuggers (Hitex or MC types), an internal pull-up resistor at the TRST_N JTAG pin is not included. The user

has to ensure the proper circuitry for the utilized debugger .

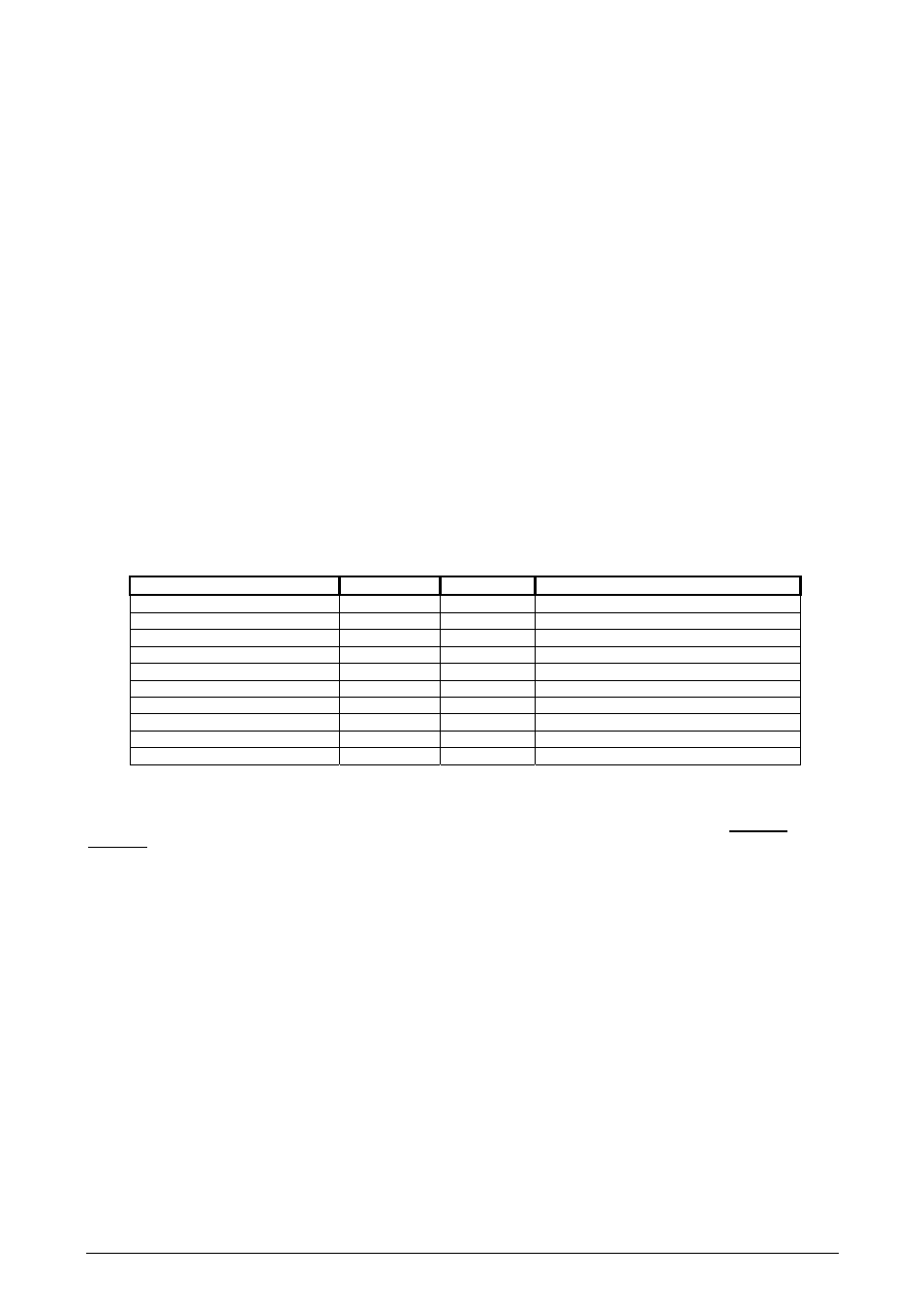

The standard connector for JTAG interfaces is a 20-pin connector with a pin spacing of 0.1 inch. All JTAG pins and the

two additional DBGREQ and DBGACK pins are connected here. The connector is assigned as follows:

Function

Pin No.

Pin No.

Function

Vcc-Sense 1

2

Vcc

TRST_N

3 4

GND

TDI 5

6

GND

TMS 7

8

GND

TCK 9

10

GND

RTCK (#1)

11

12

GND

TDO 13

14

GND

RST (#1)

15

16

GND

DBGREQ

17 18

GND

DBGACK

19 20

GND

Table 35: Pin Assignment of JTAG Interface

For connectors, pinning, signal description, and hardware circuitry for a standard JTAG interface for the multi-ICE

debugger, for example, refer to /8/.

In addition to the standard JTAG connector, the pins can also be connected to the Trace interface.

For connectors, pinning, and hardware circuitry for JTAG signals at the Trace interface, refer to /7/.

11.4 Debugging via UART

If the UART is not used for user-specific tasks, it can also be used as a debugging interface. An effective realtime

debugging is possible if the IRQ interrupt sources of the UARTare mapped to the FIQs with numbers 6 or 7. This enables

debugging of interrupt routines.

Copyright © Siemens AG 2007. All rights reserved.

95

ERTEC 200 Manual

Technical data subject to change Version 1.1.0