Arm9_ctrl, Arm9_we, Ertec 200_tag – Siemens ERTEC200 User Manual

Page 62: Phy_config

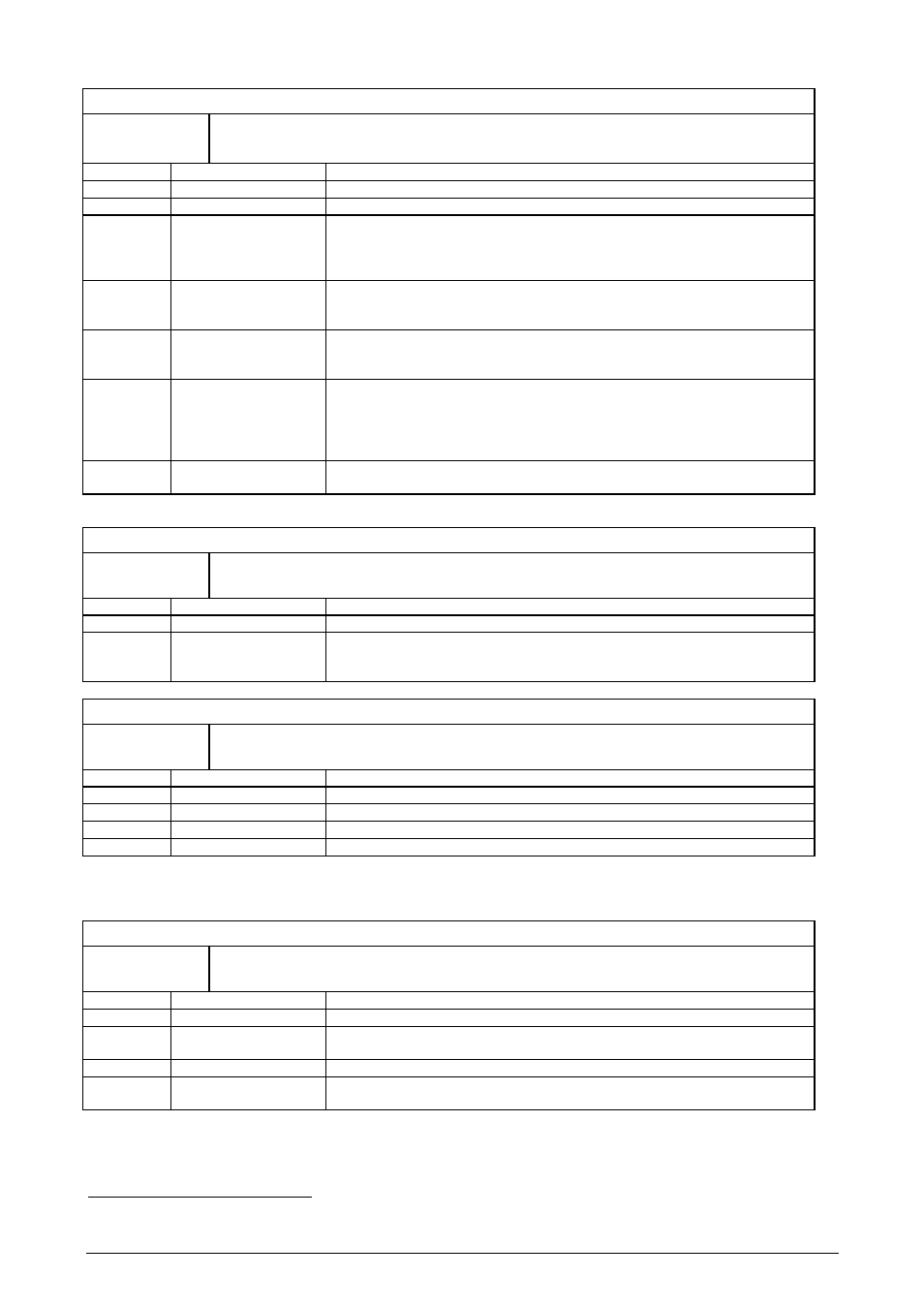

ARM9_CTRL

R/W

Addr.: 0x4000_2650

Default: 0x0000_1939

Description

Check of ARM9 inputs that are not accessible from external pins.

This register can only be written to if the Write enable bit is set in the ARM9_WE register. This

register can only be changed for debugging purposes!

Bit No.

Name

Description

31:14 Reserved

Reserved

13

BIGENDIAN

BIGENDIAN (read only)

12

DISABLE_GATE_THE

CLK

DisableGateTheClk:

1: ARM9 processor clock runs freely

0: ARM9 processor clock is paused by a Wait-for-Interrupt.

11

DBGEN

DBGEN: Enable of embedded ARM9 debugger

1: Debugger is enabled.

0: Debugger is disabled.

10

MICEBYPASS

MICEBYPASS: Bypass of TCK synchronization to the ARM9 clock.

0: TCK is synchronized to ARM 9 clock

1: TCK is not synchronized to ARM 9 clock

9

INITRAM

INITRAM: Indicates whether the TCMs are enabled after a (SW) reset.

1: TCMs enabled

0: TCMs disabled

This bit is only reset by the external RESET_N reset. SW and watchdog

resets have no effect on this bit.

8:0

SYSOPT[8:0]

ETM-Option SYSOPT(8:0): Indicates the implemented ETM options.

Default value: 139H

ARM9_WE

R/W

Addr.: 0x4000_2654

Default: 0x0000_0000

Description

Write access register for the ARM9_CTRL register

Bit No.

Name

Description

31:1 ----

Reserved

0

WE_ARM9_CTRL

Write enable for ARM9_CTL register

1: ARM9_CTRL can be write accessed.

0: ARM9_CTRL is read-only.

ERTEC 200_TAG

R/W

Addr.: 0x4000_2658

Default: 0x0001_01xx

Description

Tag number of current ASIC switching state.

Bit No.

Name

Description

31:24 Reserved

Reserved:

00h

24:16 REVISION_ID

Revision-ID:

01h

15:8 VERSION_ID Version-ID:

01h

7:0 DEBUG_ID

Debug-ID:

18h

PHY_CONFIG

R/W

Addr.: 0x4000_265C

Default: 0x0000_0000

Description

Configuration of PHY1 and PHY2

Bit No.

Name

Description

31:17

reserved

16

PHY_RES_SEL

0: PHY reset connected to chip reset like IRTE

1: PHY reset connected to IRTE output reset_phy_n

15 :14

Reserved

13

P2_AUTOMDIXEN

1: Enable AutoMDIX state machine

0: Disable AutoMDIX state machine

1

If CONFIG(6,5,2)=“111“ Bit not writeable, fix to default value.

Copyright © Siemens AG 2007. All rights reserved.

62

ERTEC 200 Manual

Technical data subject to change Version 1.1.0