Multiport ethernet phy, 9 multiport ethernet phy – Siemens ERTEC200 User Manual

Page 88

9 Multiport

Ethernet

PHY

A 2-fold multiport PHY (Physical Layer Transceiver) that supports the following transfer modes is integrated in the

ERTEC 200:

• 10BASE-T

• 100BASE-TX

• 100BASE-FX

These transfer modes are available separately for each port and can be set differently.

The PHY is compatible with the following standards:

• IEEE802.3

• IEEE802.3u

• ANSI

X3.263-1995

• ISO/IEC9314

The data interface with the Ethernet MACs takes place via MII. The management interface can be addressed via the

MDIO interface (SMI interface). The 25 MHz clock supply is to be provided as follows:

•

25 MHz quartz on the ERTEC 200 pins CLKP_A and CLKP_B or

•

25 MHz clock on the ERTEC 200 pin CLKP_A

In addition to the basic functionalities of the transfer modes 10BASE-T, 100BASE-TX, and 100BASE-FX, the PHYs also

support:

• Auto-negotiation

• Auto-crossing

• Auto-polarity

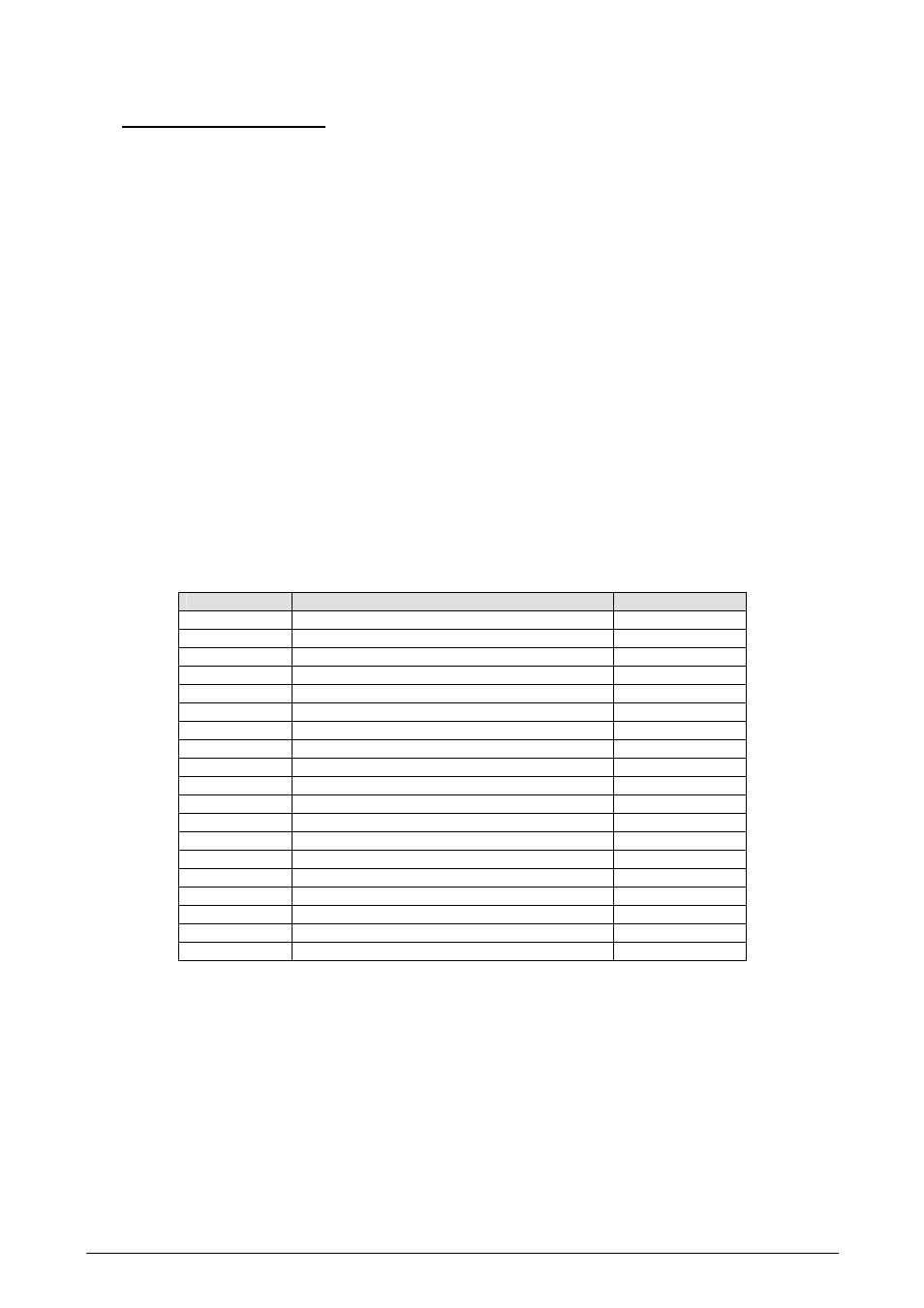

The following PHY registers can be assigned via the SMI interface:

Register-Nr.

Description

Group

0 Basic-Control-Register Basic

1 Basic-Status-Register Basic

2 PHY-Identifier

1

Extended

3 PHY-Identifier

2

Extended

4

Auto Negotiation Advertisement Register

Extended

5

Auto Negotiation Link Partner Ability Register

Extended

6

Auto Negotiation Expansion Register

Extended

7

Next Page Timing Register

Extended

8 - 15

Non-supported registers

------

16

Silicon Revision Code

Vendor-specific

17 ModeControl/

Status

Register

Vendor-specific

18 Special

Modes

Vendor-specific

19

SMII Configuration Status Register

Vendor-specific

20 - 26

Reserved

Vendor-specific

27

Control/Status Indication Register

Vendor-specific

28 Special

Internal

Testability Register

Vendor-specific

29

Interrupt Source Register

Vendor-specific

30

Interrupt mask register

Vendor-specific

31

PHY Special Control/Status Register

Vendor-specific

For an exact description of the PHY registers, refer to /13/.

During a hardware reset or when leaving the Power Down State (Px_PHY_ENB = 1), an initial configuration is set on an

internal Config port of the PHY. This configuration can be modified later in the PHY register set. The internal Config port

comprises the following parameter assignment, which at present can be permanently set or set via software in the

PHY_CONFIG system control register.

Copyright © Siemens AG 2007. All rights reserved.

88

ERTEC 200 Manual

Technical data subject to change Version 1.1.0