Memory description, Memory partitioning of the ertec 200 – Siemens ERTEC200 User Manual

Page 91

10 Memory Description

This section presents a detailed description of the memory areas of all integrated function groups.

10.1 Memory Partitioning of the ERTEC 200

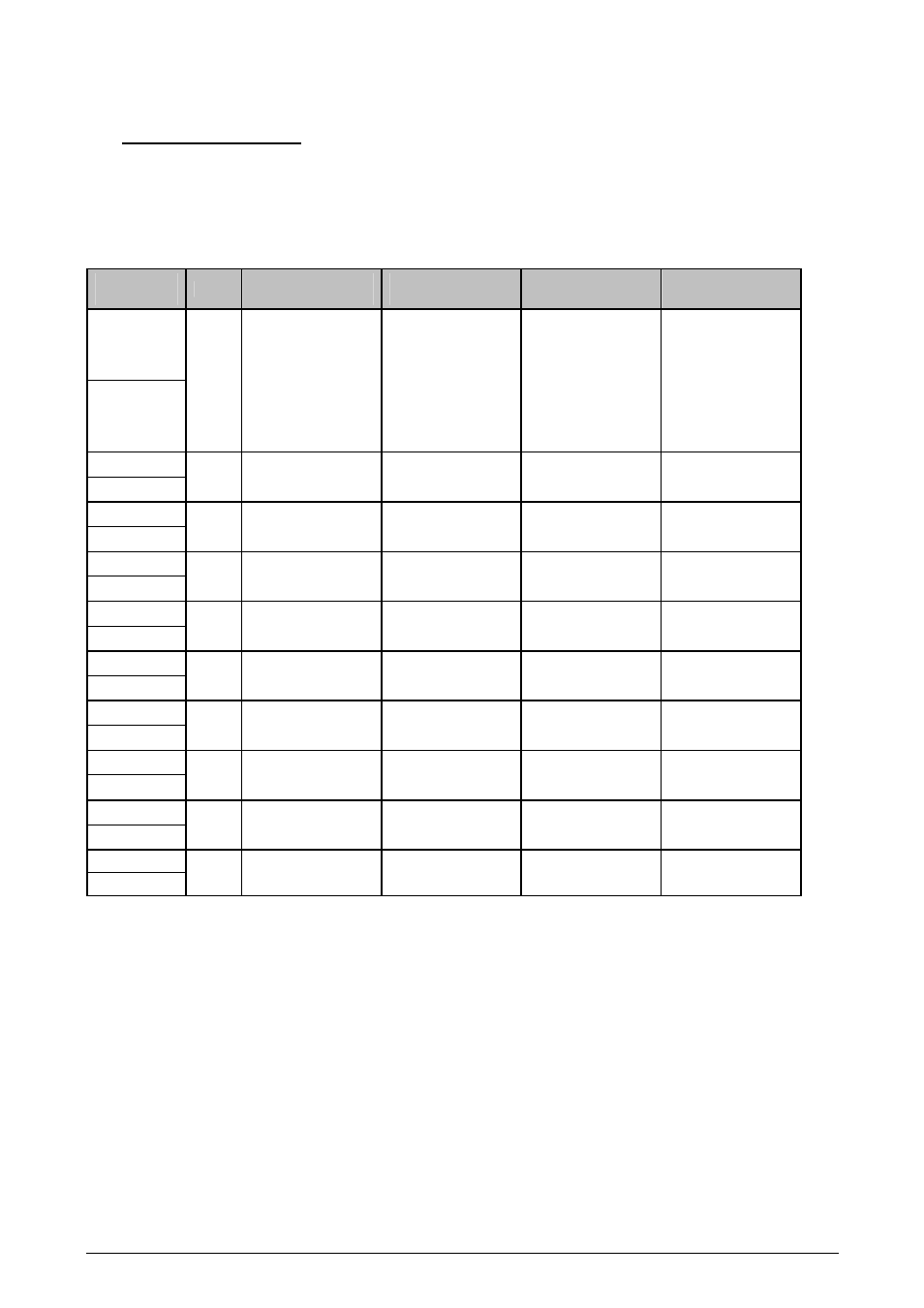

The table below lists the AHB masters along with their options for accessing various memory areas.

Start- and

Endadress

Seg.

Function Area for

ARM9

Function Area for

IRTE

Function Area for

LBU

Function Area for

DMA

0000 0000

0FFF FFFF

0

Boot ROM(0-8kB)

EMIF-SDRAM

(0-128MB)

EMIF-Memory

(0-64MB)

D-TCM(4kB)

locked I-Cache

(2/4/6kB)

Boot ROM(0-8kB)

EMIF-SDRAM

(0-128MB)

EMIF-Memory

(0-64MB)

Boot ROM(0-8kB)

EMIF-SDRAM

(0-128MB)

EMIF-Memory

(0-64MB)

Boot ROM(0-8kB)

EMIF-SDRAM

(0-128MB)

EMIF-Memory

(0-64MB)

1000 0000

1FFF FFFF

1

IRT-Switch-

Controller

IRT-Switch-

Controller

IRT-Switch-

Controller

Not used

2000 0000

2FFF FFFF

2

EMIF (SDRAM)

EMIF (SDRAM)

EMIF (SDRAM)

EMIF (SDRAM)

3000 0000

3FFF FFFF

3

EMIF

( Area: Bank 0-3)

EMIF

( Area: Bank 0-3)

EMIF

( Area: Bank 0-3)

EMIF

( Area: Bank 0-3)

4000 0000

4FFF FFFF

4

all APB interfaces

incl. Boot-ROM

Not used

all APB interfaces

incl. Boot-ROM

all APB interfaces

incl. Boot-ROM

5000 0000

5FFF FFFF

5

ARM-ICU

Not used

Not used

Not used

6000 0000

6FFF FFFF

6

Not used

Not used

Not used

Not used

7000 0000

7FFF FFFF

7 EMIF-Register

Not

used

EMIF-Register Not

used

8000 0000

8FFF FFFF

8

DMA

Not used

Not used

Not used

9000 0000

FFFF FFFF

9 - 15

Not used

Not used

Not used

Not used

Table 33: Partitioning of Memory Areas

The D-TCM with a maximum size of 4 Kbytes can be displayed on any aligned address area. The ARM946E-S then

accesses the D-TCM under this address and not the AHB bus. In addition, the locked I-cache of 2/4/6 Kbytes can be

displayed on any aligned address area.

Only the ARM946E-S can access both address areas.

IRT accesses to its own KRAM do not use the AHB bus. These accesses are implemented in the IRT switch controller.

The KRAM can be addressed starting from the memory area 0x1010_0000. An access in the non-permissible register

area is detected by an IRT-internal error signal and not by an AHB acknowledgement time-out error.

Copyright © Siemens AG 2007. All rights reserved.

91

ERTEC 200 Manual

Technical data subject to change Version 1.1.0