System control register, Address assignment of system control registers, Sspiir/sspicr – Siemens ERTEC200 User Manual

Page 58: 8 system control register

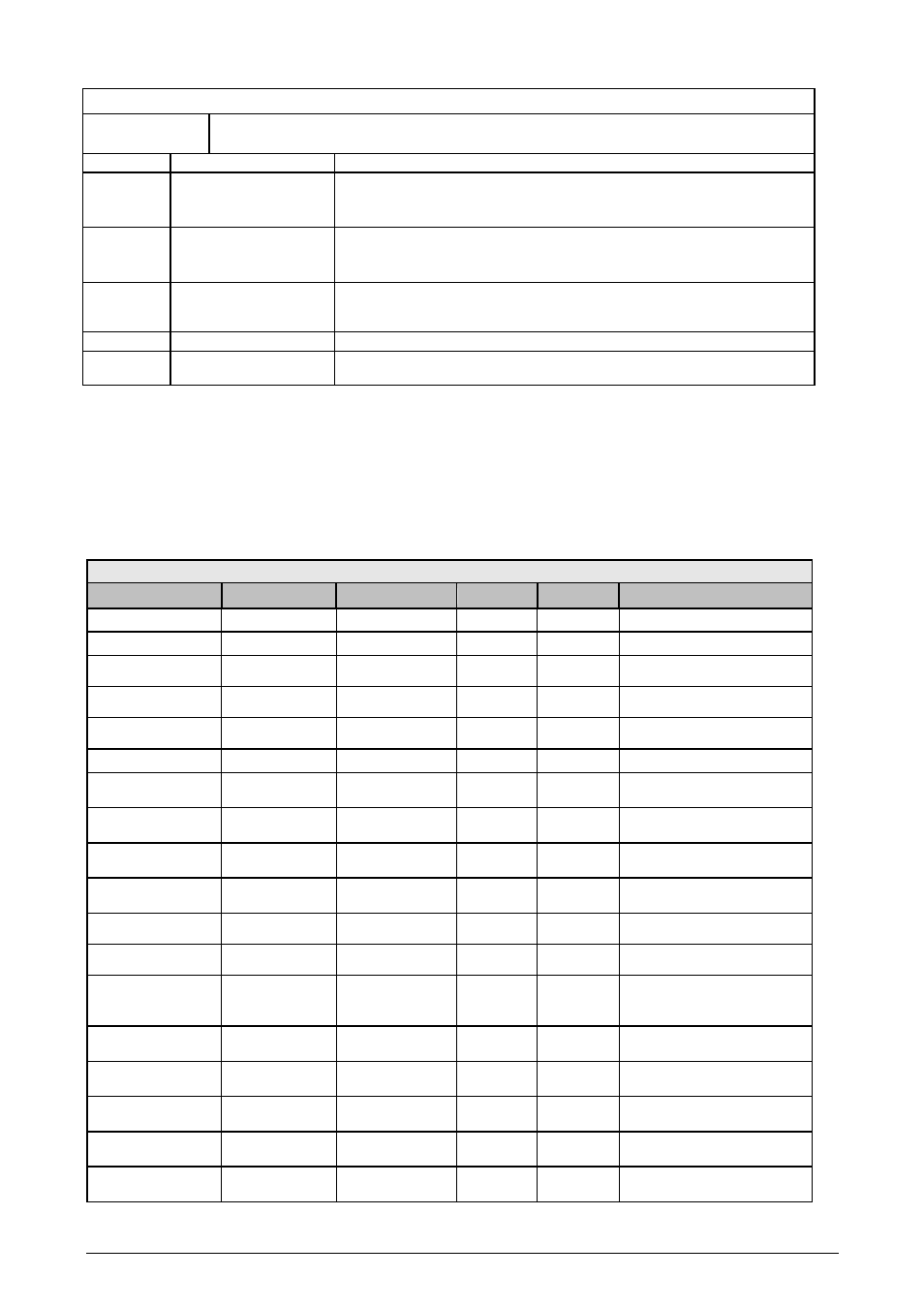

SSPIIR/SSPICR

R/W Addr.: 0x4000_2214 Default: 0x0000

Description

SPI interrupt identification register (read)

SPI interrupt clear register (write)

Bit No.

Name

Description

0

RIS (Read)

SPI Receive FIFO service request interrupt status

0 = SSPRXINTR is not active

1 = SSPRXINTR is active

1

TIS (Read)

SPI Transmit FIFO service request interrupt status

0 = SSPTXINTR is not active

1 = SSPTXINTR is active

2

RORIS (Read)

SPI Receive FIFO overrun interrupt status

0 = SSPRORINTR is not active

1 = SSPRORINTR is active

15-3 ----------

(Read)

Read: Reserved Value is undefined

15-0 ----------

(Write)

Write: Receive overrun interrupt is deleted without check to determine

whether data are currently being written.

4.8 System control register

The system control registers are ERTEC 200-specific control registers that can be read and written to from the individual

AHB masters from the APB bus. For a listing of all system control registers and their address assignments as well as a

detailed description, refer to the following sections.

4.8.1

Address Assignment of System Control Registers

The system control registers are 32 bits in width.

System Control Registers

(Base address 0x4000_2600)

Register Name

Offset Address

Address Area

Access

Default

Description

ID_REG

0x0000

4 bytes

R

0x40270100

ID ERTEC 200

BOOT_REG

0x0004

4 bytes

R

Boot-Pins

Boot mode pins Boot[3:0]

SER_CFG_REG 0x0008

4

bytes

R

Config-Pins

ERTEC 200 config pins

Config[6:1]

RES_CTRL_REG 0x000C

4

bytes

W/R

0x00000004

Control register for reset of

ERTEC 200

RES_STAT_REG 0x0010

4

bytes

R

0x00000004

Status register for reset of

ERTEC 200

PLL_STAT_REG

0x0014

4 bytes

R/W

0x00070005

Status register for PLL/FIQ3

QVZ_AHB_ADR 0x0028

4

bytes

R

0x00000000

Address of incorrect addressing

on multilayer AHB

QVZ_AHB_CTRL 0x002C

4

bytes

R

0x00000000

Control signals of incorrect

addressing on multilayer AHB

QVZ_AHB_M 0x0030 4

bytes R

0x00000000

Master detection of incorrect

addressing on multilayer AHB

QVZ_APB_ADR 0x0034

4

bytes

R

0x00000000

Address of incorrect addressing

on AHB

QVZ_EMIF_ADR 0x0038

4

bytes

R

0x00000000

Address that leads to timeout on

EMIF

MEM_SWAP 0x0044 4

bytes R/W

0x00000000

Memory Swapping in Segment 0

on the AHB bus

M_LOCK_CTRL 0x004C

4

bytes R/W

0x00000000

AHB master lock enable. Master-

selective enable of AHB lock

functionality

ARM9_CTRL 0x0050 4

bytes R/W

0x00001939

Controller of ARM9 and ETM

inputs

ARM9_WE 0x0054 4

bytes R/W

0x00000000

Write protection register for

ARM9_CTRL

ERTEC 200_TAG

0x0058

4 bytes

R

0x000101xx

TAG number of current switching

status

PHY_CONFIG 0x005C

4

bytes R/W

0x00000000

PHY1/PHY2

Configuration registers

PHY_STATUS 0x0060

4

bytes

R

0x00000000

PHY1/PHY2

Status registers

Copyright © Siemens AG 2007. All rights reserved.

58

ERTEC 200 Manual

Technical data subject to change Version 1.1.0